Процессоры и их малодокументированные функции / Блог компании Intel / Хабр

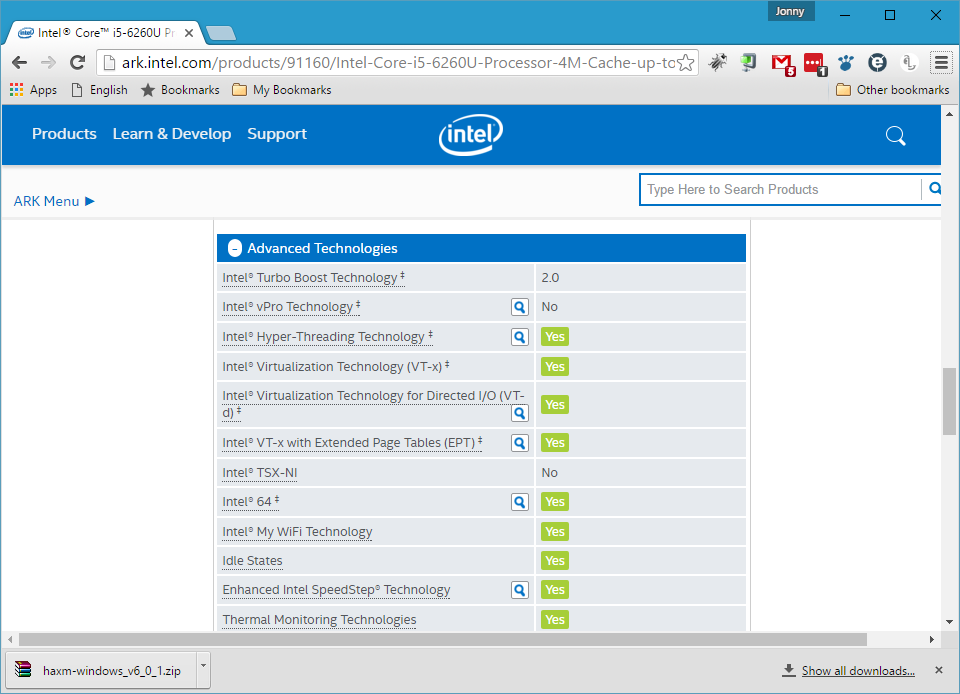

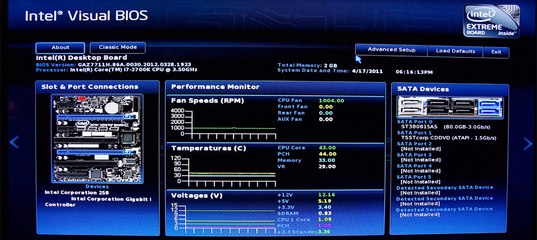

С каждым новом поколением процессоры Intel вбирают в себя все больше технологий и функций. Некоторые из них у всех на слуху (кто, например, не знает про гипертрединг?), о существовании других большинство неспециалистов даже не догадываются. Откроем всем хорошо известную базу знаний по продуктам Intel Automated Relational Knowledge Base (ARK) и выберем там какой-нибудь процессор. Мы увидим здоровенный список функций и технологий — что скрывается за их таинственными маркетинговыми наименованиями? Предлагаем углубиться в вопрос, обращая особое внимание на мало известные технологии — наверняка, там найдется много интересного.Intel Demand Based Switching

Совместно с Enhanced Intel SpeedStep Technology, технология Intel Demand Based Switching отвечает за то, чтобы в каждый момент времени при текущей загрузке процессор работал на оптимальной частоте и получал адекватное электрическое питание: не больше и не меньше, чем требуется. Таким образом уменьшается энергопотребление и тепловыделение, что актуально не только для портативных устройств, но и для серверов тоже – именно там Demand Based Switching и используется.

Таким образом уменьшается энергопотребление и тепловыделение, что актуально не только для портативных устройств, но и для серверов тоже – именно там Demand Based Switching и используется.Intel Fast Memory Access

Функция контроллера памяти для оптимизации работы с ОЗУ. Представляет собой комбинацию технологий, позволяющую благодаря углубленному анализу очереди команд выявить «совмещаемые» команды (например, чтение из одной и той же страницы памяти), а затем переупорядочить реальное выполнение таким образом, чтобы «совмещаемые» команды выполнялись друг за другом. Кроме того, менее приоритетные команды записи в память планируются на те моменты, когда прогнозируется опустошение очереди на чтение, и в результате процесс записи в память еще менее ограничивает скорость чтения.Intel Flex Memory Access

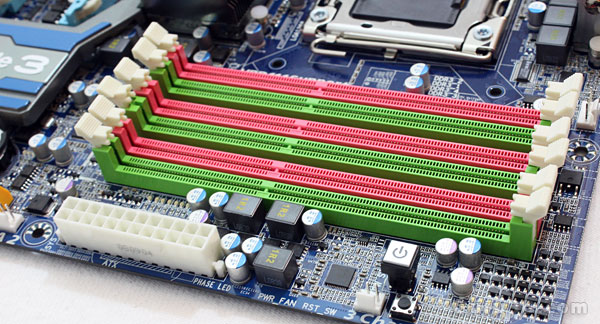

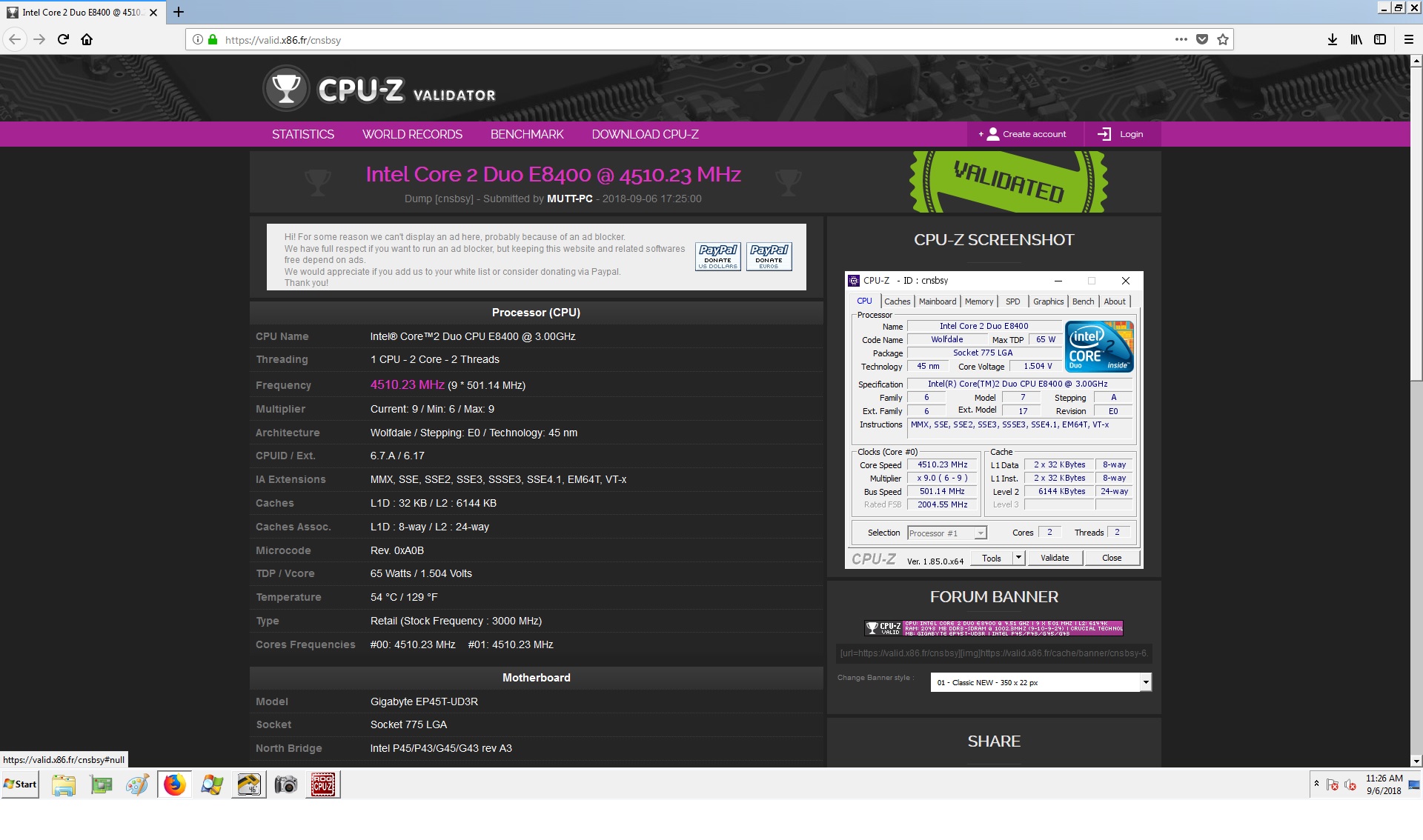

Другая функция контроллера памяти, появившаяся еще во времена, когда он представлял собой отдельный чип, в далеком 2004 году. Обеспечивает возможность работы в синхронном режиме с двумя модулями памяти одновременно, причем в отличие от простого двухканального режима, который существовал и раньше, модули памяти могут быть разного размера. Таким образом достигалась гибкость в оснащении компьютера памятью, что и отражено в названии.

Таким образом достигалась гибкость в оснащении компьютера памятью, что и отражено в названии.Intel Instruction Replay

Очень глубоко расположенная технология, появившаяся впервые в процессорах Intel Itanium. В процессе работы процессорных конвейеров может случиться такая ситуация, когда инструкции уже пришла очередь исполняться, а необходимые данные пока недоступны. Инструкцию тогда необходимо «переиграть»: снять с конвейера и запустить в его начале. Что, собственно, и происходит. Еще одна важная функция IRT – коррекция случайных ошибок на процессорных конвейерах. Подробнее об этой очень интересной функции читайте здесь.Intel My WiFi Technology

Технология виртуализации, позволяющая добавить виртуальный WiFi адаптер к существующему физическому; таким образом, ваш ультрабук или ноутбук может стать полноценной точкой доступа или повторителем. Программные компоненты My WiFi входят в состав драйвера Intel PROSet Wireless Software версии 13.2 и выше; надо иметь в виду, что с технологией совместимы лишь некоторые WiFi адаптеры. Инструкцию по установке, а также перечень программных и аппаратных совместимостей можно найти на сайте Intel.

Инструкцию по установке, а также перечень программных и аппаратных совместимостей можно найти на сайте Intel.Intel Smart Idle Technology

Еще одна технология энергосбережения. Позволяет отключать в данный момент не используемые блоки процессора или понижать их частоту. Незаменимая вещь для ЦПУ смартфона, как раз именно там и появившаяся – в процессорах Intel Atom.Intel Stable Image Platform

Термин, относящийся скорее к бизнес-процессам, нежели к технологиям. Программа Intel SIPP обеспечивает стабильность программного обеспечения, гарантируя, что основные компоненты платформ и драйверы не будут изменяться в течение, как минимум, 15 месяцев. Таким образом, корпоративные клиенты имеют возможность пользоваться одними теми же развертываемыми образами систем в течение этого срока.Intel QuickAssist

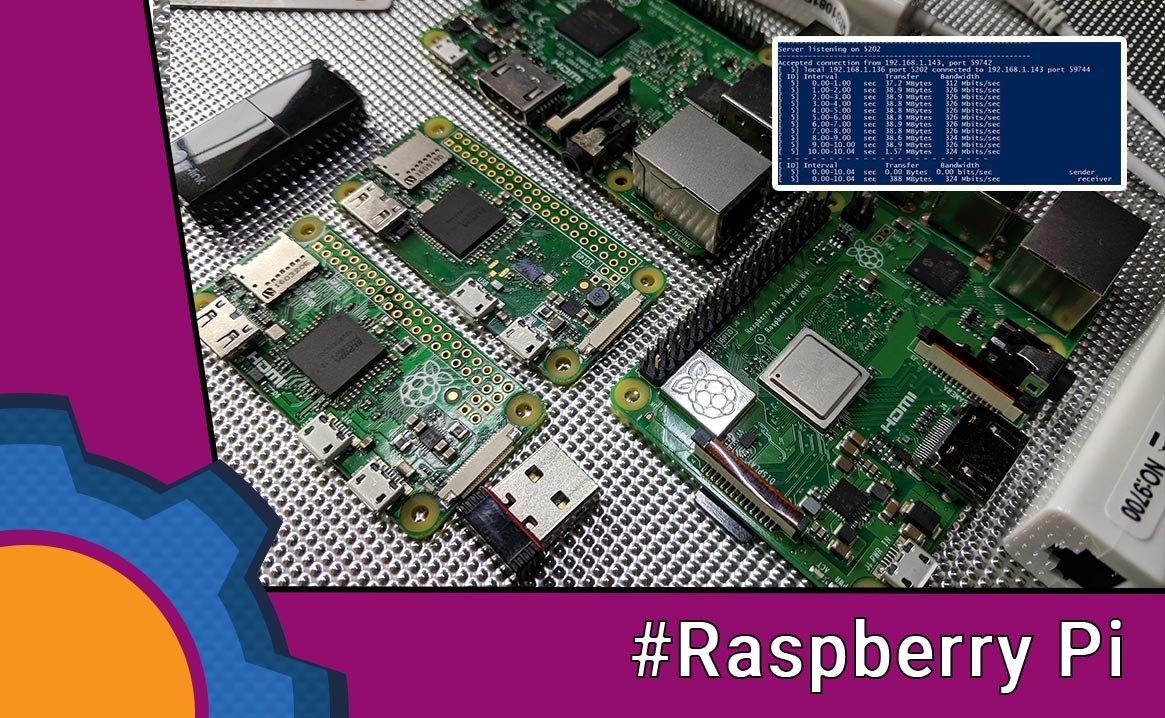

Набор аппаратно реализованных функций, требующих больших объемов вычислений, например, шифрование, компрессия, распознавание шаблонов. Смысл QuickAssist – упростить задачу разработчиков, предоставив им функциональные «кирпичики», а также ускорить их приложения. С другой стороны, технология позволяет поручить «тяжелые» задачи не самым мощным процессорам, что особенно ценится во встраиваемых системах, сильно ограниченных и по производительности, и по энергопотреблению.

С другой стороны, технология позволяет поручить «тяжелые» задачи не самым мощным процессорам, что особенно ценится во встраиваемых системах, сильно ограниченных и по производительности, и по энергопотреблению.Intel Quick Resume

Технология, разработанная для компьютеров на базе платформы Intel Viiv, позволявшая им включаться и выключаться практически мгновенно, как ТВ-приемники или DVD-плееры; при этом в «выключенном» состоянии компьютер мог продолжать выполнение некоторых задач, не требующих вмешательства пользователя. И хотя сама платформа плавно перешла в другие ипостаси вместе с сопутствовавшими ей наработками, в ARK строчка еще присутствует, ведь это было не так-то уж и давно.Intel Secure Key

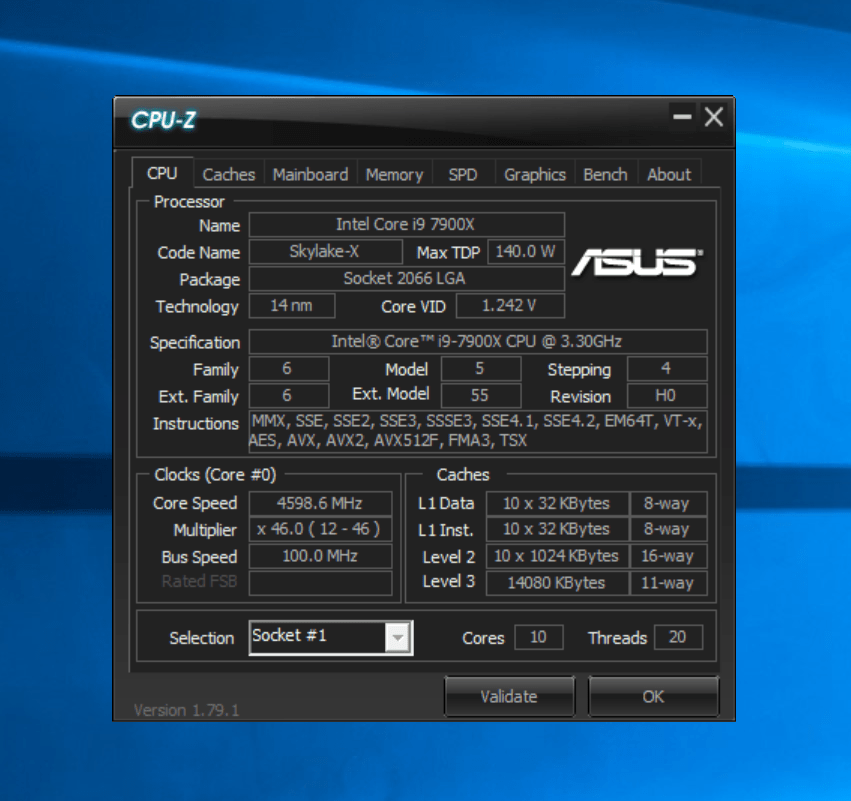

Обобщающее название для 32- и 64-битной инструкции RDRAND, использующей аппаратную реализацию генератора случайных чисел Digital Random Number Generator (DRNG). Инструкция используется в криптографических целях для генерации красивых и высококачественных случайных ключей.Intel TSX-NI

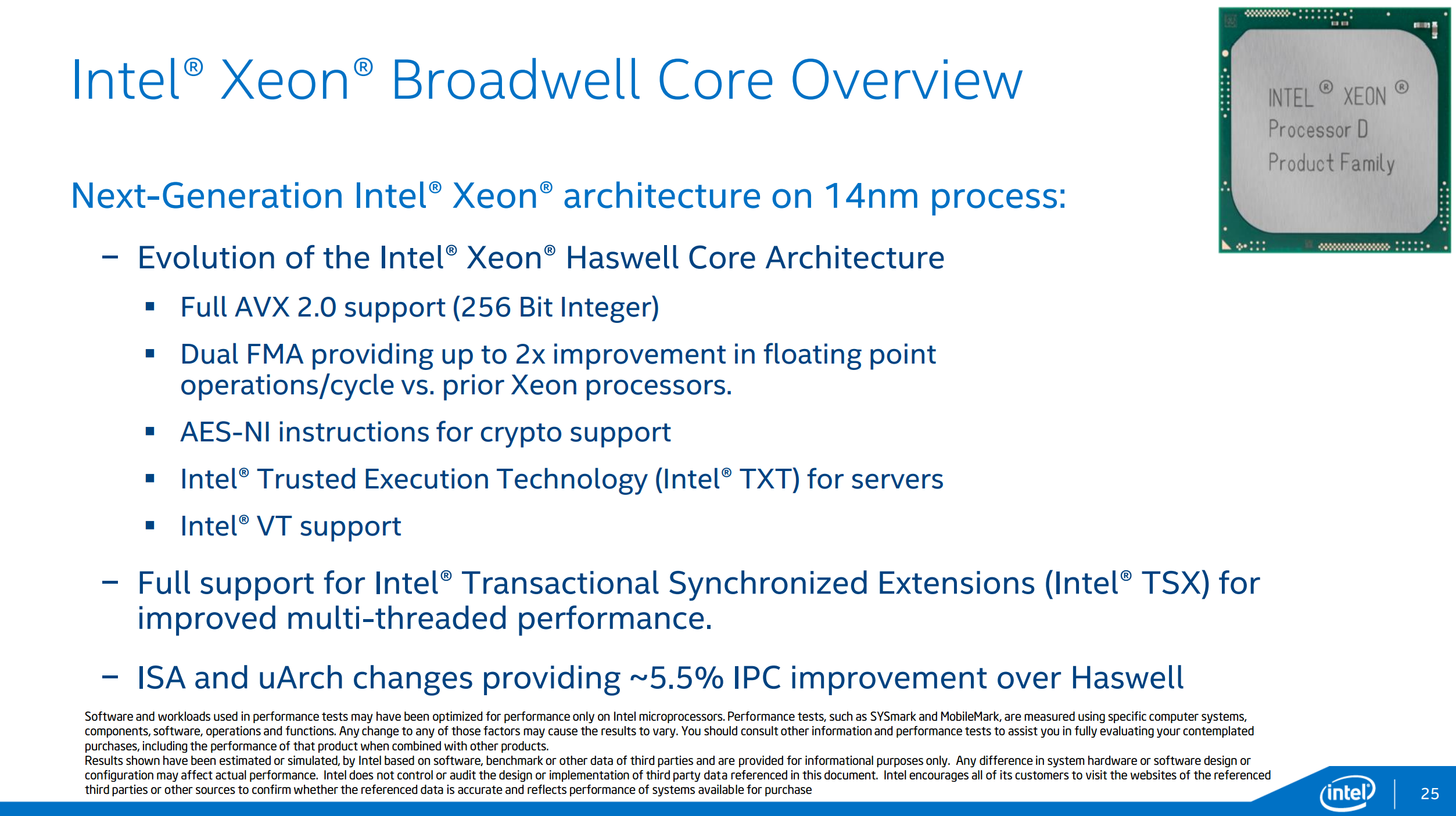

Технология со сложным названием Intel Transactional Synchronization Extensions – New Instructions подразумевает под собой надстройку над системой работы с кэшем процессора, оптимизирующую среду исполнения многопоточных приложений, но, конечно, только в том случае, если эти приложения используют программные интерфейсы TSX-NI. Со стороны пользователя данная технология непосредственным образом не видна, но все желающие могут прочитать ее описание доступным языком в блоге Степана Кольцова.

Со стороны пользователя данная технология непосредственным образом не видна, но все желающие могут прочитать ее описание доступным языком в блоге Степана Кольцова.В заключение еще раз хотим напомнить, что Intel ARK существует не только в виде сайта, но и как оффлайновое приложение для iOS и Android. Будьте в теме!

Расширения транзакционной синхронизации — Transactional Synchronization Extensions

Transactional Synchronization Extensions ( TSX ), также называемые Transactional Synchronization Extensions New Instructions ( TSX-NI ), являются расширением архитектуры набора инструкций x86 (ISA), которое добавляет аппаратную поддержку транзакционной памяти , ускоряя выполнение многопоточного программного обеспечения за счет исключения блокировки. . Согласно различным тестам, TSX / TSX-NI может обеспечить примерно на 40% более быстрое выполнение приложений при определенных рабочих нагрузках и в 4–5 раз больше транзакций базы данных в секунду (TPS).

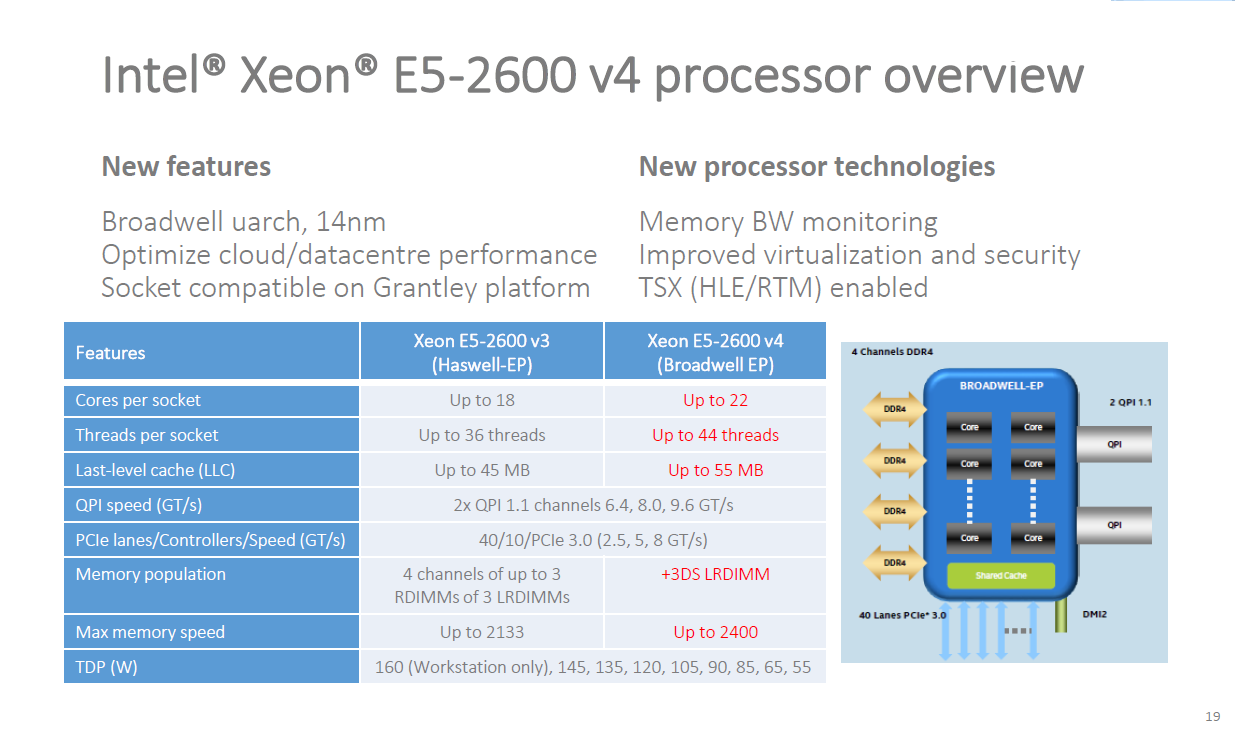

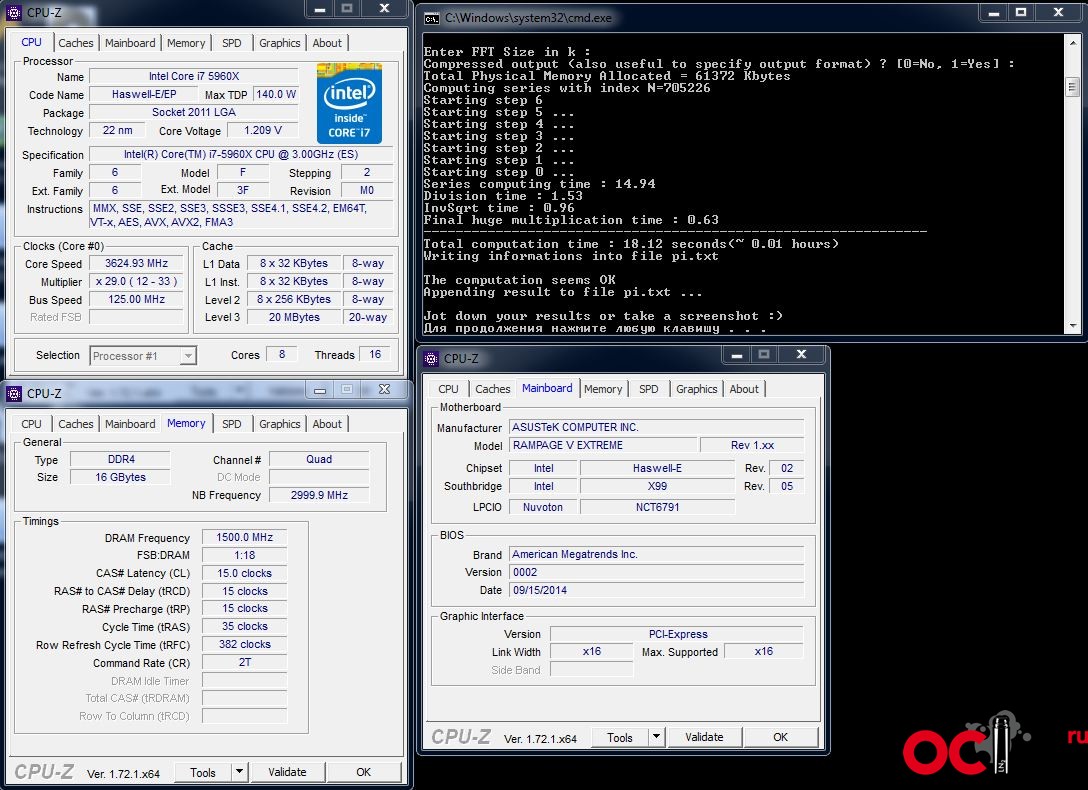

TSX / TSX-NI был задокументирован Intel в феврале 2012 года и дебютировал в июне 2013 года на некоторых микропроцессорах Intel на основе микроархитектуры Haswell . Процессоры Haswell ниже 45xx, а также R-серия и K-серия (с разблокированным множителем) SKUs не поддерживает TSX / TSX-NI. В августе 2014 года Intel объявила об ошибке в реализации TSX / TSX-NI на текущих степпингах процессоров Haswell, Haswell-E, Haswell-EP и ранних процессоров Broadwell , что привело к отключению функции TSX / TSX-NI на затронутых процессорах через обновление микрокода .

В 2016 году была обнаружена временная атака по побочному каналу путем злоупотребления способом TSX / TSX-NI обрабатывать транзакционные ошибки (то есть ошибки страниц ) для взлома KASLR во всех основных операционных системах.

Поддержка эмуляции TSX / TSX-NI предоставляется как часть эмулятора разработки программного обеспечения Intel. Также имеется экспериментальная поддержка эмуляции TSX / TSX-NI в вилке QEMU .

Особенности

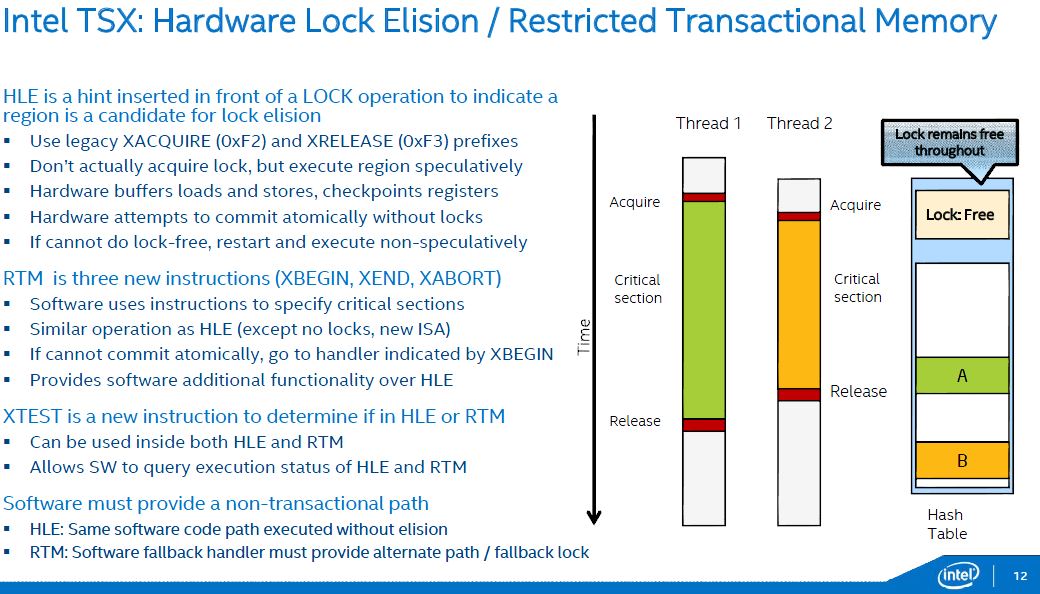

TSX / TSX-NI предоставляет два программных интерфейса для обозначения областей кода для выполнения транзакций. Hardware Lock Elision (HLE) — это интерфейс на основе префиксов инструкций, разработанный для обратной совместимости с процессорами без поддержки TSX / TSX-NI. Ограниченная транзакционная память (RTM) — это новый интерфейс набора команд, который обеспечивает большую гибкость для программистов.

TSX / TSX-NI обеспечивает оптимистичное выполнение областей транзакционного кода. Оборудование отслеживает несколько потоков на предмет конфликтующих обращений к памяти, прерывая и откатывая транзакции, которые не могут быть успешно завершены. Для программного обеспечения предусмотрены механизмы обнаружения и обработки неудачных транзакций.

Другими словами, снятие блокировки посредством выполнения транзакций использует транзакции памяти как быстрый путь, где это возможно, в то время как медленный (резервный) путь по-прежнему является нормальной блокировкой.

Аппаратный замок Elision

Hardware Lock Elision (HLE) добавляет два новых префикса инструкций XACQUIRE

XRELEASE . Эти два префикса повторно используют коды операций существующих REPNE / REPE префиксов ( F2H / F3H ). На процессорах, не поддерживающих HLE, префиксы REPNE / REPE игнорируются в инструкциях, для которых XACQUIRE / XRELEASE действительны, что обеспечивает обратную совместимость.XACQUIRE Приставка подсказку можно использовать только со следующими инструкциями с явным LOCK префиксом: ADD , ADC , AND , BTC , BTR , BTS , CMPXCHG

CMPXCHG8B , DEC , INC , NEG , NOT , OR , SBB , SUB , XOR , XADD , и XCHG .

XCHG Инструкция может быть использована без LOCK префикса , а также.XRELEASE Префикс намек может быть использован как с инструкциями , перечисленных выше, и с MOV mem, reg и MOV mem, imm инструкциями.

HLE позволяет оптимистично выполнить критический раздел, пропуская запись в блокировку, так что блокировка кажется свободной для других потоков. Неудачная транзакция приводит к перезапуску выполнения с XACQUIRE префикс отсутствовал.

Ограниченная транзакционная память

Ограниченная транзакционная память (RTM) — это альтернативная реализация HLE, которая дает программисту гибкость в указании пути резервного кода, который выполняется, когда транзакция не может быть успешно выполнена. В отличие от HLE, RTM не имеет обратной совместимости с процессорами, которые ее не поддерживают. Для обратной совместимости программы должны обнаруживать поддержку RTM в ЦП перед использованием новых инструкций.

RTM добавляет три новые инструкции: XBEGIN , XEND и XABORT . XBEGIN И XEND инструкции отмечают начало и конец транзакционного кода региона; XABORT инструкция явно прерывает транзакцию. Ошибка транзакции перенаправляет процессор на путь резервного кода, указанный в XBEGIN инструкции, со статусом прерывания, возвращаемым в EAX регистре.

Положение бита регистра EAX | Имея в виду |

|---|---|

| 0 | Устанавливается, если прерывание вызвано XABORT инструкцией. |

| 1 | |

| 2 | Устанавливается, если другой логический процессор конфликтует с адресом памяти, который был частью прерванной транзакции. |

| 3 | Устанавливается, если внутренний буфер переполнен. |

| 4 | Устанавливается, если была достигнута точка останова отладки. |

| 5 | Устанавливается, если во время выполнения вложенной транзакции произошло прерывание. |

| Зарезервированный. | |

| 31:24 | XABORT аргумент (действителен, только если установлен бит 0, в противном случае зарезервирован). |

XTEST инструкция TSX / TSX-NI предоставляет новую XTEST инструкцию, которая возвращает, выполняет ли процессор транзакционную область. Эта инструкция поддерживается процессором, если он поддерживает HLE, RTM или и то, и другое.

Отслеживание адресов приостановки TSX

TSX / TSX-NI Suspend Load Address Tracking (TSXLDTRK) — это расширение набора инструкций, которое позволяет временно отключить отслеживание загрузок из памяти в разделе кода в транзакционной области. Эта функция расширяет HLE и RTM, и ее поддержка в процессоре должна определяться отдельно.

TSXLDTRK вводит две новые инструкции XSUSLDTRK и XRESLDTRK для приостановки и возобновления отслеживания адреса загрузки соответственно. Пока отслеживание приостановлено, любые загрузки из памяти не будут добавлены к набору чтения транзакции. Это означает, что, если эти ячейки памяти не были добавлены к наборам чтения или записи транзакции за пределами области приостановки, запись в эти ячейки другими потоками не вызовет прерывания транзакции. Приостановка отслеживания адреса загрузки для части кода в транзакционной области позволяет уменьшить объем памяти, который необходимо отслеживать на предмет конфликтов чтения-записи, и, следовательно, повысить вероятность успешного принятия транзакции.

Реализация

Спецификация Intel TSX / TSX-NI описывает, как транзакционная память предоставляется программистам, но не содержит подробностей о фактической реализации транзакционной памяти. Intel указывает в своих руководствах по разработке и оптимизации, что Haswell поддерживает наборы для чтения и записи на уровне детализации строки кэша, отслеживая адреса в кэше данных L1 процессора. Intel также заявляет, что конфликты данных обнаруживаются с помощью протокола согласованности кэша .

Intel также заявляет, что конфликты данных обнаруживаются с помощью протокола согласованности кэша .

Кэш данных L1 Haswell имеет ассоциативность восемь. Это означает, что в этой реализации транзакционное выполнение, которое записывает в девять различных местоположений, отображаемых в один и тот же набор кешей, будет прервано. Однако из-за микроархитектурных реализаций это не означает, что меньшее количество обращений к одному и тому же набору гарантированно никогда не прервется. Кроме того, в конфигурациях ЦП с технологией Hyper-Threading кэш L1 используется совместно двумя потоками в одном ядре, поэтому операции в логическом процессоре одного уровня с одним и тем же ядром могут вызвать вытеснение.

Независимые исследования указывают на то, что транзакционная память Haswell, скорее всего, представляет собой систему отложенного обновления, использующую кеши для каждого ядра для транзакционных данных и контрольные точки регистрации. Другими словами, Haswell с большей вероятностью будет использовать систему транзакционной памяти на основе кеша, поскольку это гораздо менее рискованный вариант реализации.

В августе 2014 года Intel объявила о наличии ошибки в реализации TSX / TSX-NI на процессорах Haswell, Haswell-E, Haswell-EP и ранних процессорах Broadwell, что привело к отключению функции TSX / TSX-NI на затронутых процессорах с помощью микрокода. Обновить. Ошибка была исправлена в степпингах F-0 процессора Core M-5Y70 Broadwell с поддержкой vPro в ноябре 2014 года.

Ошибка была обнаружена, и о ней было сообщено во время дипломной работы в Школе электротехники и вычислительной техники Афинского национального технического университета .

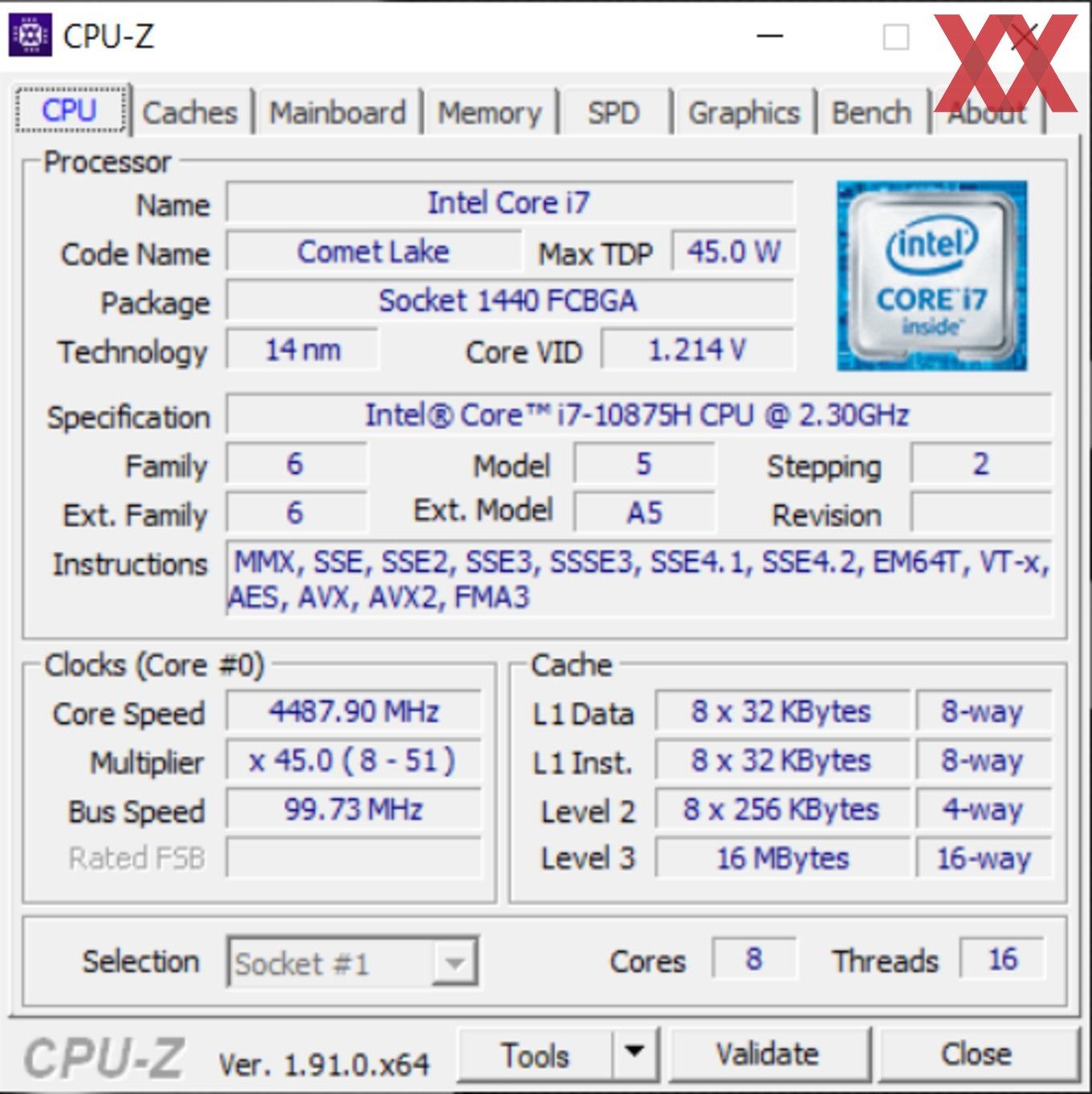

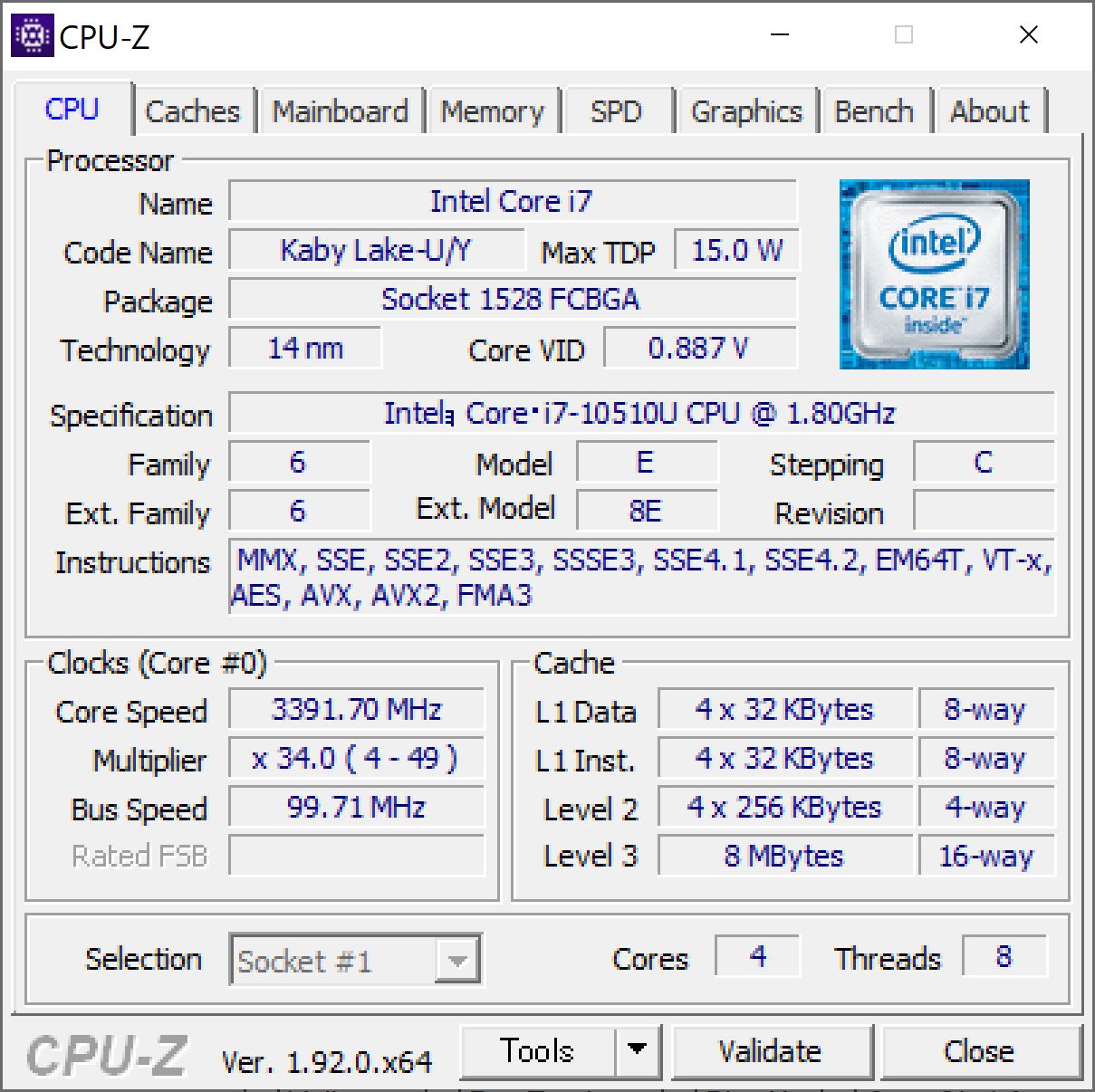

Согласно Справочному руководству по оптимизации архитектур Intel 64 и IA-32 от мая 2020 г., том 1, глава 2.5 Архитектура набора команд Intel и удаленные функции, HLE был удален из продуктов Intel, выпущенных в 2019 г. и позже. RTM не документируется как удаленная. Однако процессоры Intel Comet Lake и Ice Lake 10-го поколения , выпущенные в 2020 году, не поддерживают TSX / TSX-NI, включая HLE и RTM.

и позже. RTM не документируется как удаленная. Однако процессоры Intel Comet Lake и Ice Lake 10-го поколения , выпущенные в 2020 году, не поддерживают TSX / TSX-NI, включая HLE и RTM.

В справочнике по программированию расширений набора инструкций архитектуры Intel, редакция 41 от октября 2020 года, новое расширение набора инструкций TSXLDTRK было задокументировано и намечено для включения в будущие процессоры Sapphire Rapids .

Приложения

- RPCS3 (эмулятор PlayStation 3)

Смотрите также

Рекомендации

дальнейшее чтение

- Afek, Y .; Леви, А .; Моррисон, А. (2014). Материалы симпозиума ACM 2014 г. по принципам распределенных вычислений — PODC ’14 . Программно-улучшенная аппаратная блокировка, стр. 212. DOI : 10,1145 / 2611462,2611482 . ISBN 9781450329446 . S2CID 16645370 . . Программные улучшения аппаратной блокировки в Intel TSX.

внешние ссылки

- Презентация IDF 2012 (PDF)

- Добавление блокировки в Linux , Linux Plumbers Conference 2012 (PDF)

- Lock elision в библиотеке GNU C , LWN.net , 30 января 2013 г., Энди Клин

- Руководство по оптимизации TSX , глава 12 (PDF)

- Руководство разработчика программного обеспечения , том 1, глава 2.5 (PDF)

- Интернет-ресурсы о расширениях Intel Transactional Synchronization Extensions

- x86, микрокод: ОШИБКА: обновление микрокода, изменяющее x86_capability , LKML , сентябрь 2014 г. (есть еще один похожий отчет об ошибке )

- Микрокод Intel , Gentoo, 19 сентября 2015 г.

Отличается ли Intel ® Transactional Synchronization Extensions New Instruction (TSX-NI) от Intel TSX?

Это кажется просто маркетинговым украшением.

Я не нашел ссылок на «TSX-NI» ни в интернете, ни в руководствах Intel, ни в инструкции Intel ISA extensions.

Цитируя Intel [ 1 ]

Intel Transactional Synchronization Extensions (Intel TSX) поставляется в двух вариантах: HLE и RTM.

Благодаря их реализации эти два аспекта отделены друг от друга (каждый из них может поддерживаться отдельно от другого) и только RTM вводит новые инструкции.

Так что они, вероятно, имеют в виду RTM.

Я считаю, что HLE был введен первым, и должны быть процессоры, которые поддерживают HLE, но не RTM (обратное, хотя и возможно, кажется неправдоподобным).

Так что, может быть, это просто маркетинг правильный способ сказать: «This CPU supports our latest TSX features!».

Для справки, я написал краткое введение в две части Intel TSX, исходя из предположения, что «TSX-NI» относится к «TSX RTM».

Полная ссылка приведена в руководстве Intel 1 — Глава 15 .

HLE

В HLE (аппаратная блокировка Элизии) часть имеет обратную совместимость.

Мы все еще можем проверить его доступность с помощью CPUID.07H.EBX.HLE[bit 4], но он реализуется путем изменения семантики префиксов repne / repe для инструкций.

Эта функция состоит из двух префиксов «new»: xacquire и xrelease .

Теперь CPU способен входить в транзакционное состояние, в котором каждое чтение добавляется к набору чтения транзакции, а каждая запись добавляется к набору записи транзакции и не выполняется в память.

Гранулярность-это размер строки кэша.

Если поток считывает данные из набора для чтения или записывает данные в набор для чтения или в набор для записи другого потока, то транзакция прерывается.

CPU восстанавливает архитектурное состояние, как оно было в начале транзакции, и повторно выполняет инструкции без транзакций.

Если транзакция завершается успешно, вся записанная память фиксируется полностью атомарно.

Транзакции делятся на xacquire и xrelease .

Они могут гнездиться, но существует ограничение на глубину (выше которой транзакция прерывается) и на количество различных блокировок, которые могут быть отменены (превышено, что CPU не будет удалять новые блокировки, но не будет прерывать транзакцию).

Когда вложенная транзакция прерывается, CPU перезапускает выполнение самой внешней транзакции.

xacquire (код операции F2 , такой же, как repne ) используется перед инструкцией, которая получит блокировку (т. е. запись в блокировку) и отмечает начало транзакции.

Это чтение не добавляется в набор записи (или параллелизм не может произойти, поскольку каждый поток записывает блокировку, и это немедленно прервало бы любую последующую транзакцию).

Вместо этого он добавляется в набор для чтения.

xrelease (код операции F3 ) используется перед инструкцией, которая освобождает блокировку и отмечает окончание транзакции. xrelease должен использоваться на той же блокировке, которая используется с xacquire для сопряжения с ней и завершения транзакции.

xacquire можно использовать только с версией lock d этих инструкций: ADD, ADC, AND, BTC, BTR, BTS, CMPXCHG, CMPXCHG8B, DEC, INC, NEG, NOT, OR, SBB, SUB, XOR, XADD, XCHG .

xrelease с теми же инструкциями плюс MOV mem, reg и MOV mem, imm без префикса lock .

Новая инструкция xtest доступна, если HLE (или RTM) присутствует, он устанавливает ZF является процессор не находится внутри транзакции.

RTM

RTM (ограниченная транзакционная память) не имеет обратной совместимости.

Его можно протестировать с помощью CPUID.07H.EBX.RTM [бит 11].

Он вводит три новые инструкции: xbegin, xend и xabort .

Они представляют собой просто новый интерфейс для уже заданной и общей возможности выполнения транзакций.

xbegin должен предоставлять в качестве относительного смещения указатель на путь резервного кода.

Этот код выполняется всякий раз, когда транзакция не может быть зафиксирована.

В таких случаях eax содержит причину прерывания.

xend завершает транзакцию и дает команду CPU зафиксировать ее. xabort позволяет программисту прервать транзакцию явно с помощью пользовательского кода ошибки.

Intel не дает никаких гарантий относительно способности процессора успешно совершить транзакцию.

В то время как HLE имеет набор очень специфических условий, RTM является функцией типа «best effort» — таким образом, требование для резервного кода.

RTM является более низкоуровневым, чем HLE, он позволяет программисту использовать транзакционную память, с использованием или без использования блокировок.

Смешивание HLE и RTM

Цитируя Intel:

Поведение, когда HLE и RTM вложены вместе—HLE inside RTM или RTM inside HLE-это конкретная реализация. Однако, во всех случаях, реализация будет поддерживать семантику HLE и RTM. Реализация может выберите игнорировать подсказки HLE при использовании внутри областей RTM и может вызвать прерывание транзакции, когда инструкции RTM используются внутри областей HLE.

В последнем случае, переход от транзакционной к нетранзакционных выполнение происходит плавно так как процессор будет повторно выполнять область HLE без фактического выполнения elision, и затем выполните инструкции RTM.

Технологии INTEL

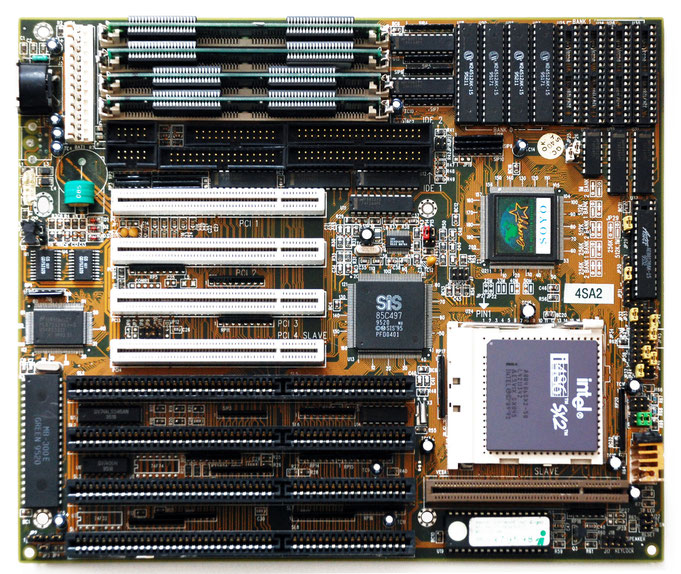

Intel Corporation — это корпорация, которая уже много лет (с 1968 г.) производит большое количество электронных устройств и компьютерного оборудования: процессоры, системные платы, наборы микросхем, серверная продукция, продукция для сетей Ethernet, беспроводные решения и многое другое. У компании INTEL создано громадное количество технологий, которые являются яркой чертой знака качества производимых электронных шедевров!

Так как технологий от Intel очень много, предлагаю рассмотреть только малую часть, которые могут заинтересовать обычного пользователя. Каждая технология уникальна, поэтому позволяет насладится преимуществом производительности, мобильности, энергоэффективности, вычислительной мощности и защитой данных. Более подробную информацию можно получить на официальном сайте производителя: Официальный сайт Intel. Итак, пора рассмотреть передовые технологии, встроенные технологии визуализации, технологии защиты и данных INTEL.

Более подробную информацию можно получить на официальном сайте производителя: Официальный сайт Intel. Итак, пора рассмотреть передовые технологии, встроенные технологии визуализации, технологии защиты и данных INTEL.

Встроенное ПО Intel Management Engine (Intel ME) использует встроенные возможности платформы и приложений управления и безопасности для удаленного внеполосного управления сетевыми вычислительными ресурсами.

Звуковая подсистема Intel High Definition Audio поддерживает воспроизведение большего количества каналов в более высоком качестве, чем предыдущие интегрированные аудиосистемы. Кроме того, в звуковую подсистему Intel High Definition Audio интегрированы технологии, необходимые для поддержки самых новых форматов звука.

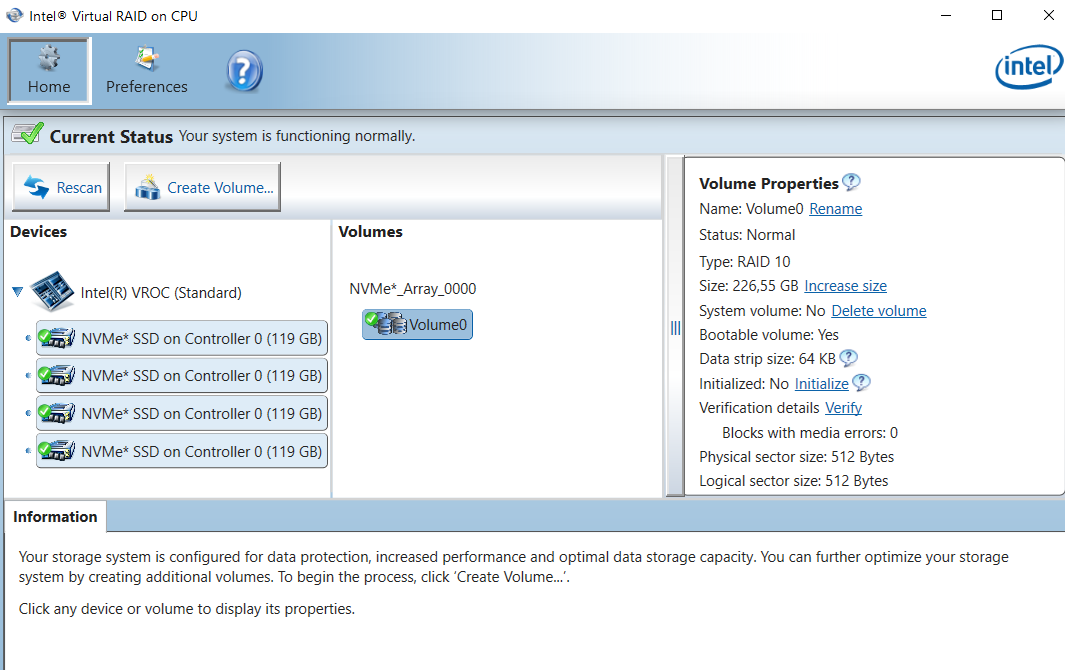

Технология Intel Matrix Storage обеспечивает защиту, производительность и расширяемость платформ настольных и мобильных ПК. Пользователи, использующие один или несколько жестких дисков, получают преимущество дополнительной производительности и более низкое энергопотребление. При использовании нескольких дисков пользователь получает дополнительную защиту от потери данных на случай сбоя жесткого диска. Предшественница технологии хранения.

При использовании нескольких дисков пользователь получает дополнительную защиту от потери данных на случай сбоя жесткого диска. Предшественница технологии хранения.

Технология Intel Rapid Start поддерживается некоторыми моделями устройств Ultrabook, оснащенных процессорами Intel Core. Она позволяет за считанные секунды вывести Ultrabook из спящего режима, возвратив его в состояние, в котором вы его оставили.

Технология Intel Smart Connect обеспечивает автоматическое обновление содержимого электронной почты и социальных сетей, когда компьютер находится в режиме сна. Благодаря технологии Intel Smart Connect вам не придется ожидать загрузки обновленной информации после пробуждения компьютера.

Технология Intel Smart Response сочетает высокую производительность небольших твердотельных накопителей с большим объемом жесткого диска.

Программа Intel Stable Image Platform (Intel SIPP) может помочь вашей компании находить и внедрять стандартизированные, стабильные платформы ПК в течение как минимум 15 месяцев.

Технология «Преимущества для малого бизнеса Intel» предлагает компаниям малого бизнеса комплексное решение для повышения безопасности и производительности благодаря таким функциям, как программный мониторинг, резервное копирование и восстановление данных, блокировщик порта USB, центр технического состояния ПК и технология Wireless Display.

Расширения набора команд — это дополнительные инструкции, с помощью которых можно повысить производительность при выполнении операций с несколькими объектами данных. К ним относятся SSE (Поддержка расширений SIMD) и AVX (Векторные расширения).

Intel Demand Based Switching — это технология управления питанием, в которой прикладное напряжение и тактовая частота микропроцессора удерживаются на минимальном необходимом уровне, пока не потребуется увеличение вычислительной мощности. Эта технология была представлена на серверном рынке под названием Intel SpeedStep.

Технология Intel Virtualization для направленного ввода/вывода для Itanium (VT-i) позволяет одной платформе процессора Intel Itanium функционировать в качестве нескольких «виртуальных» платформ. Технология улучшает возможности управления, снижая время простоев и поддерживая продуктивность работы за счет выделения отдельных разделов для вычислительных операций.

Технология улучшает возможности управления, снижая время простоев и поддерживая продуктивность работы за счет выделения отдельных разделов для вычислительных операций.

Технология Intel Hyper-Threading Technology обеспечивает два потока обработки для каждого физического ядра. Многопоточные приложения могут выполнять больше задач параллельно, что значительно ускоряет выполнение работы.

Технология Intel Turbo Boost динамически увеличивает частоту процессора до необходимого уровня, используя разницу между номинальным и максимальным значениями параметров температуры и энергопотребления, что позволяет увеличить эффективность энергопотребления или при необходимости «разогнать» процессор.

Технология Intel vPro представляет собой встроенный в процессор комплекс средств управления и обеспечения безопасности, предназначенный для решения задач в четырех основных областях информационной безопасности: 1) Управление угрозами, включая защиту от руткитов, вирусов и другого вредоносного ПО 2) Защита личных сведений и точечная защита доступа к веб-сайту 3) Защита конфиденциальных личных и деловых сведений 4) Удаленный и местный мониторинг, внесение исправлений, ремонт ПК и рабочих станций.

Технология Intel Virtualization для направленного ввода/вывода (VT-x) позволяет одной аппаратной платформе функционировать в качестве нескольких «виртуальных» платформ. Технология улучшает возможности управления, снижая время простоев и поддерживая продуктивность работы за счет выделения отдельных разделов для вычислительных операций.

Технология Intel Virtualization Technology для направленного ввода/вывода дополняет поддержку виртуализации в процессорах на базе архитектуры IA-32 (VT-x) и в процессорах Itanium (VT-i) функциями виртуализации устройств ввода/вывода. Технология Intel Virtualization для направленного ввода/вывода помогает пользователям увеличить безопасность и надежность систем, а также повысить производительность устройств ввода/вывода в виртуальных средах.

Intel VT-x с технологией Extended Page Tables, известной также как технология Second Level Address Translation (SLAT), обеспечивает ускорение работы виртуализованных приложений с интенсивным использованием памяти. Технология Extended Page Tables на платформах с поддержкой технологии виртуализации Intel сокращает непроизводительные затраты памяти и энергопотребления и увеличивает время автономной работы благодаря аппаратной оптимизации управления таблицей переадресации страниц.

Технология Extended Page Tables на платформах с поддержкой технологии виртуализации Intel сокращает непроизводительные затраты памяти и энергопотребления и увеличивает время автономной работы благодаря аппаратной оптимизации управления таблицей переадресации страниц.

Intel Transactional Synchronization Extensions New Instructions (Intel TSX-NI) представляют собой набор команд, ориентированных на масштабирование производительности в многопоточных средах. Эта технология помогает более эффективно осуществлять параллельные операции с помощью улучшенного контроля блокировки ПО.

Архитектура Intel 64 в сочетании с соответствующим программным обеспечением поддерживает работу 64-разрядных приложений на серверах, рабочих станциях, настольных ПК и ноутбуках. Архитектура Intel 64 обеспечивает повышение производительности, за счет чего вычислительные системы могут использовать более 4 ГБ виртуальной и физической памяти.

Технология Intel My WiFi обеспечивает беспроводное подключение Ultrabook или ноутбука к устройствам с поддержкой WiFi, таким как принтеры, стереосистемы и т. д.

д.

Усовершенствованная технология Intel SpeedStep позволяет обеспечить высокую производительность, а также соответствие требованиям мобильных систем к энергосбережению. Стандартная технология Intel SpeedStep позволяет переключать уровень напряжения и частоты в зависимости от нагрузки на процессор. Усовершенствованная технология Intel SpeedStep построена на той же архитектуре и использует такие стратегии разработки, как разделение изменений напряжения и частоты, а также распределение и восстановление тактового сигнала.

Технологии термоконтроля защищают корпус процессора и систему от сбоя в результате перегрева с помощью нескольких функций управления температурным режимом. Внутрикристаллический цифровой термодатчик температуры (Digital Thermal Sensor — DTS) определяет температуру ядра, а службы управления температурным режимом при необходимости снижают энергопотребление корпусом процессора, тем самым уменьшая температуру, для обеспечения работы в пределах нормальных эксплуатационных характеристик.

Технология Intel Clear Video HD поддерживает воспроизведение видео в формате HD, повышая качество изображения в играх и фильмах, воспроизведение дисков Blue-ray и потоковых трансляций через Интернет.

Технология Intel Insider позволяет передавать премиум-контент в формате HD на Ultrabook и ПК.

Технология Intel InTRU 3D позволяет воспроизводить трехмерные стереоскопические видеоматериалы в формате Blu-ray с разрешением 1080p, используя интерфейс HDMI 1.4 и высококачественный звук, а также обеспечивает трехмерное изображение в играх и другом мультимедийном контенте.

Графическое решение Intel Iris — это новейшая и самая мощная графическая технология Intel, встроенная непосредственно в процессоры Intel Core 4-го поколения. Обеспечивая удвоение производительности по сравнению с предыдущими графическими технологиями Intel. Не менее эффектно Intel Iris работает при воспроизведении фильмов высокого (HD) и сверхвысокого (4К) разрешения.

Графическое решение Intel HD Graphics — графическая технология, встроенная в процессоры Intel Core 2-го и 3-го поколений. Это решение обеспечивает высокопроизводительную графику и функции обработки мультимедиа на уровне процессора, заметно увеличивая быстродействие и позволяя не устанавливать дополнительный графический адаптер, при этом не требуя для него дополнительное пространство.

Технология Intel Quick Sync Video обеспечивает быстрое кодирование и декодирование видео. Позволяет оперативно создавать диски DVD или Blu-ray, редактировать видео, преобразовывать видеофайлы для портативного проигрывателя мультимедиа и видео для размещения в сети.

Технология Intel Wireless Display (Intel WiDi) упрощает трансляцию фильмов, видеороликов, фотографий, музыки, приложений и другого контента на большой экран телевизора. По беспроводному подключению на телевизор можно выводить контент с жесткого диска, домашней сети, Интернета. Перед просмотром нужно лишь подключить адаптер к телевизору и выполнить несколько простых действий. Чтобы воспользоваться технологией Intel Wireless Display, требуются ноутбук и телевизионный адаптер, поддерживающие эту технологию.

Перед просмотром нужно лишь подключить адаптер к телевизору и выполнить несколько простых действий. Чтобы воспользоваться технологией Intel Wireless Display, требуются ноутбук и телевизионный адаптер, поддерживающие эту технологию.

Advanced Encryption Standard New Instructions (AES-NI) представляют собой набор команд, позволяющий быстро и безопасно обеспечить шифрование и расшифровку данных. Команды AES-NI могут применяться для решения широкого спектра криптографических задач, например, в приложениях, обеспечивающих групповое шифрование, расшифровку, аутентификацию, генерацию случайных чисел и аутентифицированное шифрование.

Технология Intel Secure Key представляет собой генератор случайных чисел, создающий уникальные комбинации для усиления алгоритмов шифрования.

Технология Intel Trusted Execution расширяет возможности безопасного исполнения команд посредством аппаратного расширения возможностей процессоров и наборов микросхем Intel . Эта технология обеспечивает для платформ цифрового офиса такие функции защиты, как измеряемый запуск приложений и защищенное выполнение команд. Это достигается за счет создания среды, где приложения выполняются изолированно от других приложений системы.

Эта технология обеспечивает для платформ цифрового офиса такие функции защиты, как измеряемый запуск приложений и защищенное выполнение команд. Это достигается за счет создания среды, где приложения выполняются изолированно от других приложений системы.

Бит отмены выполнения — это аппаратная функция безопасности, которая позволяет уменьшить уязвимость к вирусам и вредоносному коду, а также предотвратить выполнение вредоносного ПО и его распространение на сервере или в сети.

Технология Intel для защиты от краж (Anti-Theft) помогает обеспечить безопасность данных на переносном компьютере в случае, если его потеряли или украли. Для использования технологии Intel для защиты от краж необходимо получить подписку у поставщика услуги технологии Intel для защиты от краж.

Технология защиты конфиденциальности Intel (Intel Identity Protection) — встроенная технология безопасности, основанная на использовании токенов. Эта технология предоставляет простые и надежные средства контроля доступа к коммерческим и бизнес-данным в режиме онлайн, обеспечивая защиту от угроз безопасности и мошенничества. Технология защиты конфиденциальности Intel использует аппаратные механизмы аутентификации ПК на веб-сайтах, в банковских системах и сетевых службах, подтверждая уникальность данного ПК, защищает от несанкционированного доступа и предотвращает атаки с использованием вредоносного ПО.

Технология защиты конфиденциальности Intel использует аппаратные механизмы аутентификации ПК на веб-сайтах, в банковских системах и сетевых службах, подтверждая уникальность данного ПК, защищает от несанкционированного доступа и предотвращает атаки с использованием вредоносного ПО.

Core i7-8706G стал единственным из Kaby Lake-G с поддержкой vPro

Недавно представленные трёхкристальные процессоры Intel Kaby Lake-G привлекли внимание многих из тех, кто интересуется современным «железом». В дни проведения выставки CES 2018 состоялся анонс не только моделей Core i7-8809G, Core i7-8709G, Core i7-8705G и Core i5-8305G, но и ещё одного процессора, о котором не было упомянуто в официальной документации 8 января, — Core i7-8706G. Если вышеупомянутая четвёрка предназначена для включения в состав компактных игровых десктопов, ноутбуков и «2-в-1», то CPU с индексом 8706G может не только порадовать геймеров достойным уровнем производительности в рамках 65 Вт TDP, но и помочь интегрировать использующий его компьютер в корпоративную ИТ-инфраструктуру.

Ближайшим родственником Core i7-8706G является процессор Core i7-8705G. Характеристики этих чипов совпадают почти во всём, но «8706-й» при прочих равных всё же предпочтительнее ввиду поддержки технологий Intel vPro и Trusted Execution (TXT), набора инструкций TSX-NI и программы Stable Image Platform (SIPP).

С помощью vPro может осуществляться интеграция ПК в корпоративную сеть. Данная технология улучшает защиту данных как на программном, так и аппаратном уровнях, кроме того, значительно упрощается процедура установки единого пакета ПО для рабочих мест, планирование и установка обновлений и т. д. На первый взгляд, игровому компьютеру с Core i7-8706G на борту это ни к чему, но, например, для его эксплуатации в тестовой лаборатории vPro может пригодится. Ещё одна возможность — использование домашнего ПК (ноутбука, «2-в-1») на работе, где требуется взаимодействие с другими компьютерами посредством vPro.

Intel TXT обеспечивает безопасность платформы, а надстройка TSX-NI — оптимизацию среды исполнения многопоточных приложений, которые используют программные интерфейсы TSX-NI. Наконец, SIPP гарантирует сохранность сочетаний ключевых компонентов платформ и актуальность драйверов в течение 15 месяцев либо до выхода нового поколения процессоров.

Наконец, SIPP гарантирует сохранность сочетаний ключевых компонентов платформ и актуальность драйверов в течение 15 месяцев либо до выхода нового поколения процессоров.

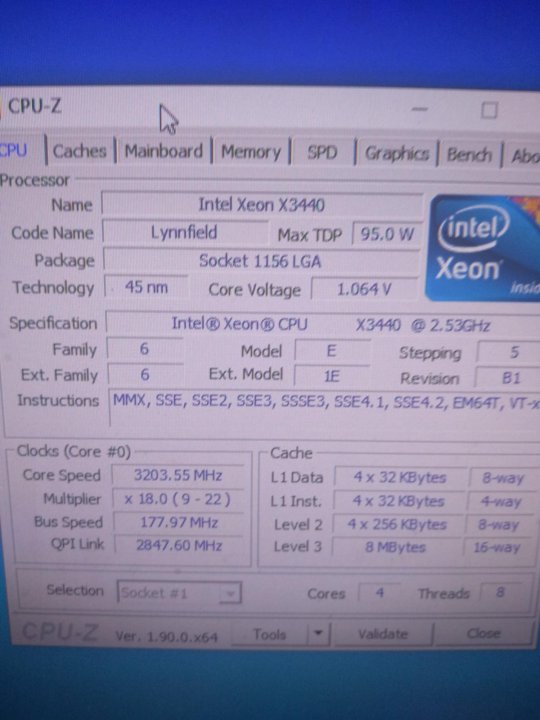

В арсенале модели Core i7-8706G (конструктив — BGA2270) значатся четыре вычислительных ядра с частотой от 3,1 до 4,1 ГГц, 8 Мбайт кеш-памяти третьего уровня, двухканальный контроллер оперативной памяти DDR4-2400, тепловой пакет 65 Вт, поддержка технологий Turbo Boost 2.0 и Hyper-Threading. Графических ядра у рассматриваемого CPU два — довольно скромное, соседствующее с x86-ядрами, Intel HD 630 с частотой 350–1100 МГц и производительное дискретное AMD Radeon RX Vega M GL. Последнее оперирует 1280 потоковыми процессорами GCN 5-го поколения с частотой от 931 до 1011 МГц и взаимодействует с 4-Гбайт микросхемой буферной памяти HBM2 с 1024-битной шиной и пропускной способностью 179,2 Гбайт/с.

Цены на процессоры Kaby Lake-G компания Intel пока не оглашала. Выход первых серийных устройств на основе Core i7-8809G, Core i7-8706G и других представителей вышеназванного семейства CPU состоится весной.

Если вы заметили ошибку — выделите ее мышью и нажмите CTRL+ENTER.

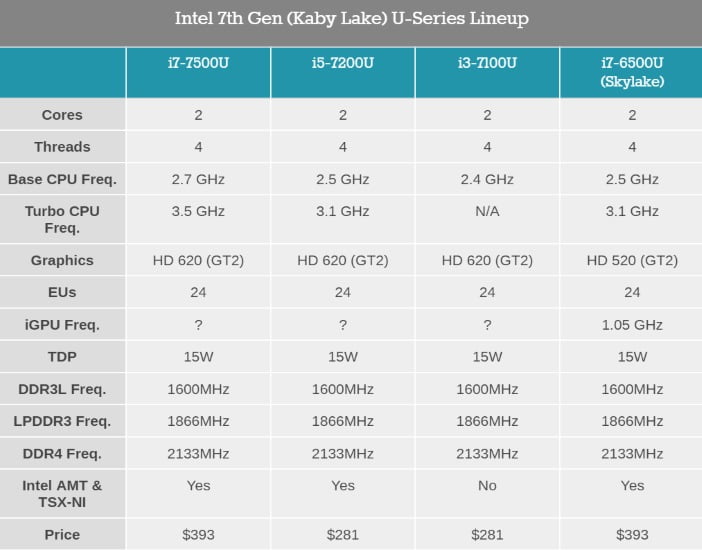

| Частота ядра станд./макс. GHz | Стандартная рабочая частота всех ядер / Максимальная частота ядер в режиме Turbo Boost 2.0, в GHz |

| Ядер / потоков | Количество физических ядер / вычислительных потоков или логических CPU, которое «видит» операционная система |

| Кэш L3, MB | Объем кэш-памяти L3 в MB |

| DDR3, эффект.частота | Максимальная эффективная рабочая частота памяти DDR3 в MHz |

| Макс.объем ОЗУ, GB | Максимальный поддерживаемый объем оперативной памяти в GB в двухканальном режиме |

| Поддержка ECC | Поддержка технологии контроля четности (ECC) для коррекции однобитных ошибок памяти |

| TDP, Вт | Максимальное тепловыделение процессора, Вт |

Intel® Turbo Boost 2. 0 0 | Технология Intel® Turbo Boost автоматически повышает частоту ядер процессора в пределах разрешенного теплового пакета |

| Intel® Hyper-Threading | Технология Intel® Hyper-Threading позволяет ядру процессора выполнять два вычислительных потока одновременно, что значительно ускоряет работу многопоточных приложений |

| Intel® Smart Cache | Технология Intel® Smart Cache динамически распределяет кэш-память 3-го уровня между ядрами процессора в зависимости от их загрузки |

| Intel® AES-NI | Advanced Encryption Standard New Instructions (AES-NI) — набор инструкций процессора, которые обеспечивают быстрое и надежное шифрование данных по стандарту AES |

| Intel® Vpro | Технология Intel® Vpro включает аппаратные средства защиты и дистанционного управления компьютером |

| Intel® VT-x | Технология Intel® Virtualization (Intel® VT-x) обеспечивает аппаратную поддержку виртуализации со стороны процессора, повышая производительность и надежность |

| Intel® VT-d | Технология Intel® Virtualization Technology for Directed I/O (Intel® VT-d) повышает производительность устройств ввода/вывода в виртуальных средах |

| Intel® VT-x EPT | Технология Intel® VT-x Extended Page Tables (Intel® VT-x EPT) обеспечивает ускорение работы виртуализованных приложений с интенсивным использованием памяти |

| Intel® TSX-NI | Технология Intel® Transactional Synchronization Extensions New Instructions (Intel® TSX-NI) ускоряет выполнение параллельных операций с помощью контроля блокировки ПО |

| Intel® TXT | Технология Intel® Trusted Execution ( Intel® TXT) — это набор аппаратных расширений для процессора и чипсета с соответствующим ПО для повышения безопасности платформы |

| Intel® AVX | Технология Intel® Advanced Vector Extensions (Intel® AVX) — набор команд для повышения производительности вычислений за счет ипользования операций над векторами |

| Intel® My WiFi | Технология Intel® My WiFi обеспечивает беспроводное подключение к устройствам с поддержкой WiFi, таким как принтеры, стереосистемы и т. д. д. |

| Overclocking | Возможность повышения тактовой частоты процессора за счет изменения процессорного множителя |

| Intel® SpeedStep® | Технология Intel® SpeedStep® позволяет автоматически переключать уровень напряжения и частоты процессора в зависимости от нагрузки |

| Термоконтроль | Технологии термоконтроля защищают процессор и систему от сбоя в результате перегрева с помощью функций управления температурным режимом |

| Intel® SIPP | Программа Intel® Stable Image Platform (Intel ® SIPP) обеспечивает стандартизацию аппаратной платформы ПК на протяжении как минимум 15 месяцев |

| Intel® HD Graphics | Версия встроенного в процессор графического ядра Intel® HD Graphics |

Ст./макс. частота, MHz частота, MHz | Номинальная тактовая частота рендеринга графики / Максимальная динамическая частота рендеринга с функцией Dynamic Frequency (МГц) |

| Объем памяти, GB | Максимальный объем видеопамяти графической системы |

| Intel® Quick Sync Video | Технология Intel® Quick Sync Video обеспечивает быструю конвертацию видео для медиапроигрывателей, размещения в сети, а также редактирования и создания видео |

| Intel® InTru™ 3D | Технология Intel® InTRU™ 3D позволяет воспроизводить трехмерные стереоскопические видеоматериалы в формате Blu-ray* с разрешением 1080p, используя интерфейс HDMI* 1.4 и высококачественный звук |

| Intel® Insider™ | Технология Intel® Insider™ позволяет передавать премиум-контент в формате HD на Ultrabook™ и ПК |

| Intel® Wireless Display | Технология Intel® Wireless Display обеспечивает передачу по беспроводной сети фильмов, фотографий, веб-сайтов и других данных на HDTV-монитор |

| Intel® Clear Video HD | Технология Intel® Clear Video HD поддерживает воспроизведение видео в формате HD, повышая качество изображения в играх и фильмах |

Поддерж. дисплеев дисплеев | Число поддерживаемых дисплеев |

| Intel® Core™ | торговая марка |

| i7 | серия |

| 2 | номер поколения процессоров Intel Core |

| 600 | индекс производительности |

| К | буквенный суффикс |

| Процессор Intel® Xeon® Gold 6242 (22 МБ кэш-памяти, 2,80 ГГц) | |

| Основные данные | |

| Коллекция продукции | Масштабируемый процессор Intel® Xeon® 2-го поколения |

| Кодовое название | Продукция с прежним кодовым названием Cascade Lake |

| Вертикальный сегмент | Server |

| Процессор Номер | 6242 |

| Состояние | Launched |

| Дата выпуска | Q2’19 |

| Литография | 14 nm |

| Рекомендуемая цена для клиента | $1273.00 — $1280.00 |

| Производительность | |

| Количество ядер | 16 |

| Количество потоков | 32 |

| Базовая тактовая частота процессора | 2,80 GHz |

| Максимальная тактовая частота с технологией Turbo Boost | 3,90 GHz |

| Кэш-память | 22MB |

| Количество каналов UPI | 3 |

| Расчетная мощность | 150 W |

| Дополнительная информация | |

| Доступные варианты для встраиваемых систем | Нет |

| Спецификации памяти | |

Макс. объем памяти (зависит от типа памяти) объем памяти (зависит от типа памяти) | 1 TB |

| Типы памяти | DDR4-2933 |

| Максимальная скорость памяти | 2933 MHz |

| Макс. число каналов памяти | 6 |

| Поддержка памяти ECC ‡ | Да |

| Поддержка энергонезависимой памяти Intel® Optane™ DC | Да |

| Варианты расширения | |

| Масштабируемость | 4S |

| Редакция PCI Express | 3,0 |

| Макс. кол-во каналов PCI Express | 48 |

| Спецификации корпуса | |

| Поддерживаемые разъемы | FCLGA3647 |

| TCASE | 85°C |

| Размер корпуса | 76.0mm x 56.5mm |

| Усовершенствованные технологии | |

| Технология Intel® Deep Learning Boost (Intel® DL Boost) | Да |

| Технология Intel® Speed Select Technology (Intel® SST) — профиль производительности | Нет |

| Технология Intel® Speed Select Technology (Intel® SST) — базовая частота | Нет |

| Технология Intel® Resource Director Technology (Intel® RDT) | Да |

| Технология Intel® Speed Shift | Да |

Технология Intel® Turbo Boost Max 3. 0 ‡ 0 ‡ | Нет |

| Технология Intel® Turbo Boost ‡ | 2,0 |

| Соответствие платформе Intel® vPro™ ‡ | Да |

| Технология Intel® Hyper-Threading ‡ | Да |

| Технология виртуализации Intel® (VT-x) ‡ | Да |

| Технология виртуализации Intel® для направленного ввода/вывода (VT-d) ‡ | Да |

| Intel® VT-x с таблицами Extended Page Tables (EPT) ‡ | Да |

| Intel® TSX-NI | Да |

| Архитектура Intel® 64 ‡ | Да |

| Расширения набора команд | Intel® SSE4.2, Intel® AVX, Intel® AVX2, Intel® AVX-512 |

| Количество модулей AVX-512 FMA | 2 |

| Усовершенствованная технология Intel SpeedStep® | Да |

| Технология Intel® Volume Management Device (VMD) | Да |

| Безопасность и надежность | |

| Новые команды Intel® AES | Да |

| Технология Intel® Trusted Execution ‡ | Да |

| Функция Бит отмены выполнения ‡ | Да |

| Технология Intel® Run Sure | Да |

| Управление выполнением на основе режимов (MBE) | Да |

Overview

Intel® Transactional Synchronization Extensions (Intel® TSX) позволяют процессору динамически определять, нужно ли потокам сериализоваться через защищенные блокировкой критические секции, и выполнять сериализацию только при необходимости. Это позволяет процессору обнаруживать и использовать параллелизм, скрытый в приложении из-за динамически ненужной синхронизации.

Это позволяет процессору обнаруживать и использовать параллелизм, скрытый в приложении из-за динамически ненужной синхронизации.

В Intel® TSX указанные программистом области кода (также называемые транзакционными областями) выполняются транзакционно.Если транзакционное выполнение завершается успешно, то все операции с памятью, выполняемые в транзакционной области, будут казаться происходящими мгновенно при просмотре с других логических процессоров. Процессор делает обновления архитектуры, выполняемые в области, видимыми для других логических процессоров только при успешной фиксации, этот процесс называется атомарной фиксацией.

Intel® TSX также обеспечиваетИнструкция XTEST

, позволяющая программному обеспечению запрашивать, выполняет ли логический процессор транзакции в транзакционной области, идентифицированной либо с помощью аппаратной блокировки (HLE), либо с помощью ограниченной транзакционной памяти (RTM). Поскольку успешное выполнение транзакции обеспечивает атомарную фиксацию, процессор оптимистично выполняет область кода без явной синхронизации. Если для этого конкретного выполнения в синхронизации не было необходимости, выполнение можно зафиксировать без какой-либо межпоточной сериализации. Если процессор не может выполнить атомарную фиксацию, оптимистичное выполнение не удастся. Когда это происходит, процессор откатывает выполнение, и этот процесс называется прерыванием транзакции. При прерывании транзакции процессор отменяет все обновления, выполненные в регионе, восстанавливает архитектурное состояние так, как если бы оптимистическое выполнение никогда не происходило, и возобновляет выполнение без транзакций.

Если для этого конкретного выполнения в синхронизации не было необходимости, выполнение можно зафиксировать без какой-либо межпоточной сериализации. Если процессор не может выполнить атомарную фиксацию, оптимистичное выполнение не удастся. Когда это происходит, процессор откатывает выполнение, и этот процесс называется прерыванием транзакции. При прерывании транзакции процессор отменяет все обновления, выполненные в регионе, восстанавливает архитектурное состояние так, как если бы оптимистическое выполнение никогда не происходило, и возобновляет выполнение без транзакций.

Процессор может выполнить прерывание транзакции по многим причинам. Основная причина связана с конфликтующим доступом между логическим процессором, выполняющим транзакции, и другим логическим процессором. Такие конфликтующие обращения могут помешать успешному выполнению транзакции. Адреса памяти, считываемые из транзакционной области, составляют набор для чтения транзакционной области, а адреса, записанные в транзакционной области, составляют набор записи транзакционной области. Intel® TSX поддерживает наборы для чтения и записи с точностью до строки кэша. Конфликтующий доступ возникает, если другой логический процессор либо читает местоположение, которое является частью набора записи транзакционной области, либо записывает местоположение, которое является частью набора для чтения или записи транзакционной области.

Intel® TSX поддерживает наборы для чтения и записи с точностью до строки кэша. Конфликтующий доступ возникает, если другой логический процессор либо читает местоположение, которое является частью набора записи транзакционной области, либо записывает местоположение, которое является частью набора для чтения или записи транзакционной области.

Конфликтный доступ обычно означает, что для этой области кода требуется сериализация. Intel® TSX обнаруживает конфликты данных на уровне детализации строки кэша, поэтому несвязанные местоположения данных, помещенные в одну и ту же строку кэша, будут обнаружены как конфликты.Транзакционные прерывания также могут происходить из-за ограниченных транзакционных ресурсов. Объем данных, к которым осуществляется доступ в регионе, может превышать емкость, зависящую от реализации. Некоторые инструкции и системные события также могут вызывать прерывание транзакции. Частые прерывания транзакций приводят к потере циклов.

Intel® TSX предоставляет два программных интерфейса для указания областей кода для выполнения транзакций.

Hardware Lock Elision (HLE)

HLE — это расширение набора команд, совместимое с предыдущими версиями (включаяXACQUIRE

ипрефиксы XRELEASE

) для указания транзакционных регионов.HLE предназначен для программистов, которые предпочитают обратную совместимость традиционной модели программирования с взаимным исключением и хотели бы запускать программное обеспечение с поддержкой HLE на устаревшем оборудовании, но хотели бы воспользоваться преимуществами новых возможностей исключения блокировок на оборудовании с поддержкой HLE. Встроенные функцииHardware Lock Elision (HLE) применимы только к приложениям C / C ++ для Windows *.

Ограниченная транзакционная память (RTM)

RTM — это новый интерфейс набора команд (включающийXBEGIN

,XEND

иXABORT

) для программистов, чтобы определять транзакционные области более гибким образом, чем это возможно с HLE. RTM предназначена для программистов, которые предпочитают гибкий интерфейс аппаратному обеспечению для выполнения транзакций.

c ++ — Отличается ли новая инструкция Intel® Transactional Synchronization Extensions (TSX-NI) от Intel TSX?

Кажется, это просто маркетинговое украшение.

Я не нашел ссылок на «TSX-NI» ни в Интернете, ни в руководствах Intel, ни в руководстве по расширениям Intel ISA.

Цитата Intel [1]

Intel Transactional Synchronization Extensions (Intel TSX) поставляется в двух вариантах: HLE и RTM.

Из-за своей реализации эти два аспекта разделены (один может поддерживаться отдельно от другого), и только RTM вводит новые инструкции.

Значит, они, вероятно, имеют в виду RTM.

Я считаю, что HLE был представлен первым, и должны быть процессоры, поддерживающие HLE, но не RTM (обратное, хотя и возможно, кажется неправдоподобным).

Так что, возможно, это просто маркетинговый правильный способ сказать: «Этот процессор поддерживает наши новейшие функции TSX!».

Для справки, я написал краткое введение в две части Intel TSX, исходя из предположения, что «TSX-NI» относится к «TSX RTM».

Полную справку можно найти в Intel Manual 1 — Chapter 15 .

HLE

Часть HLE (Hardware Lock Elision) имеет обратную совместимость.

Мы все еще можем проверить его доступность с помощью CPUID.07H.EBX.HLE [bit 4] , но это реализовано путем изменения семантики префиксов repne / repeat для инструкций.

Эта функция состоит из двух «новых» префиксов: xacquire и xrelease .

Теперь ЦП может входить в состояние транзакции, в котором каждое чтение добавляется к набору чтения транзакции, а каждая запись добавляется к набору записи транзакции и не выполняется в память.

Гранулярность — это размер строки кэша.

Если поток читает из набора чтения или записывает в набор чтения или набор записи другого потока, то транзакция прерывается.

ЦП восстанавливает архитектурное состояние, которое было в начале транзакции, и повторно выполняет инструкции без транзакции.

Если транзакция завершается успешно, вся записанная память фиксируется атомарно.

Транзакции ограничены кодами xacquire и xrelease .

Они могут быть вложенными, но существует ограничение на глубину (выше которой транзакция прерывается) и на количество различных блокировок, которые могут быть отменены (превышено, что ЦП не отменяет новые блокировки, но не прерывает транзакцию) .

Когда вложенная транзакция прерывается, ЦП перезапускает выполнение самой внешней транзакции .

xacquire (код операции F2 , такой же, как repne ) используется перед инструкцией, которая получит блокировку (то есть записывает в блокировку) и отмечает начало транзакции.

Это чтение — это , а не , добавленное к набору записи (или может не произойти параллелизм, поскольку каждый поток записывает в блокировку, и это немедленно прерывает любую последующую транзакцию).

Вместо этого добавляется в набор для чтения.

xrelease (код операции F3 ) используется перед инструкцией, которая снимает блокировку и отмечает окончание транзакции.

xrelease должен использоваться на той же блокировке, что и xacquire , для сопряжения с ним и завершения транзакции.

xacquire может использоваться только с блокировкой . d версии этих инструкций: ADD, ADC, AND, BTC, BTR, BTS, CMPXCHG, CMPXCHG8B, DEC, INC, NEG, NOT, OR, SBB, SUB, XOR, XADD, XCHG .

xrelease с теми же инструкциями плюс MOV mem, reg и MOV mem, imm без префикса lock .

Новая инструкция xtest доступна, если присутствует HLE (или RTM), она устанавливает ZF , если процессор , а не внутри транзакции.

RTM

RTM (ограниченная транзакционная память) не имеет обратной совместимости.

Его можно протестировать с CPUID. 07H.EBX.RTM [бит 11] .

07H.EBX.RTM [бит 11] .

Он вводит три новые инструкции: xbegin , xend и xabort .

Это просто новый интерфейс к уже заданной и общей возможности выполнения транзакций.

xbegin должен предоставлять в качестве относительного смещения указатель на путь резервного кода.

Этот код выполняется всякий раз, когда транзакция не может быть зафиксирована.

В таких случаях eax содержит причину прерывания.

xend завершает транзакцию и инструктирует ЦП зафиксировать ее.

xabort позволяет программисту явно прервать транзакцию с помощью специального кода ошибки.

Intel не дает никаких гарантий относительно способности процессора успешно выполнить транзакцию.

В то время как HLE имеет набор очень специфических условий, RTM — это функция «максимального усилия» — следовательно, требование для резервного кода.

RTM является более низкоуровневой версией, чем HLE, она позволяет программисту использовать транзакционную память с использованием блокировок или без них.

Смешивание HLE и RTM

Цитата Intel:

Поведение, когда HLE и RTM вложены вместе — HLE внутри RTM или RTM внутри HLE — зависит от реализации.Однако во всех случаях реализация будет поддерживать семантику HLE и RTM. Реализация может выберите игнорировать подсказки HLE при использовании внутри областей RTM и может вызвать прерывание транзакции, когда инструкции RTM используются внутри областей HLE. В последнем случае, переход от транзакционного к нетранзакционному исполнению происходит плавно поскольку процессор повторно выполнит область HLE без фактического выполнения исключения, и затем выполните инструкции RTM.

Haswell’s TSX — Разбираемся с Intel Haswell Transactional Synchronization eXtensions

Haswell’s TSX

Новые расширения Transactional Synchronization eXtensions (TSX) расширяют x86 ISA двумя новыми интерфейсами: HLE и RTM.

Ограниченная транзакционная память (RTM) использует Xbegin и Xend, что позволяет разработчикам отмечать начало и конец критического раздела. ЦП будет обрабатывать этот фрагмент кода как атомарную транзакцию. Xbegin также указывает путь возврата в случае сбоя транзакции. Либо все идет хорошо, и код выполняется без какой-либо блокировки, либо общие переменные, над которыми работает поток, перезаписываются. В этом случае код отменяется и транзакция не выполняется. Теперь ЦП выполнит обратный путь, который, скорее всего, представляет собой фрагмент кода, выполняющий грубую блокировку.Программное обеспечение с поддержкой RTM будет работать только на Haswell и, следовательно, не имеет обратной совместимости, поэтому может пройти некоторое время, прежде чем эта форма аппаратной транзакционной памяти будет принята.

ЦП будет обрабатывать этот фрагмент кода как атомарную транзакцию. Xbegin также указывает путь возврата в случае сбоя транзакции. Либо все идет хорошо, и код выполняется без какой-либо блокировки, либо общие переменные, над которыми работает поток, перезаписываются. В этом случае код отменяется и транзакция не выполняется. Теперь ЦП выполнит обратный путь, который, скорее всего, представляет собой фрагмент кода, выполняющий грубую блокировку.Программное обеспечение с поддержкой RTM будет работать только на Haswell и, следовательно, не имеет обратной совместимости, поэтому может пройти некоторое время, прежде чем эта форма аппаратной транзакционной памяти будет принята.

Самый интересный интерфейс на ближайшее время — Hardware Lock Elision или HLE. Впервые он появился в статье Рави Раджвара и Джеймса Гудмана в 2001 году. Рави сейчас является архитектором процессоров в Intel и вместе со своим коллегой Мартином Диксоном TSX представлял на IDF2012.

Идея состоит в том, чтобы снять блокировки и позволить процессору позаботиться о согласованности. Вместо того чтобы предполагать, что поток всегда должен защищать общие данные от других потоков, вы оптимистично предполагаете, что другие потоки не будут перезаписывать переменные, над которыми поток работает (в критическом разделе). Если другой поток все равно перезаписывает одну из этих общих переменных, весь процесс будет прерван ЦП, и транзакция будет повторно выполнена , но с традиционной блокировкой .

Вместо того чтобы предполагать, что поток всегда должен защищать общие данные от других потоков, вы оптимистично предполагаете, что другие потоки не будут перезаписывать переменные, над которыми поток работает (в критическом разделе). Если другой поток все равно перезаписывает одну из этих общих переменных, весь процесс будет прерван ЦП, и транзакция будет повторно выполнена , но с традиционной блокировкой .

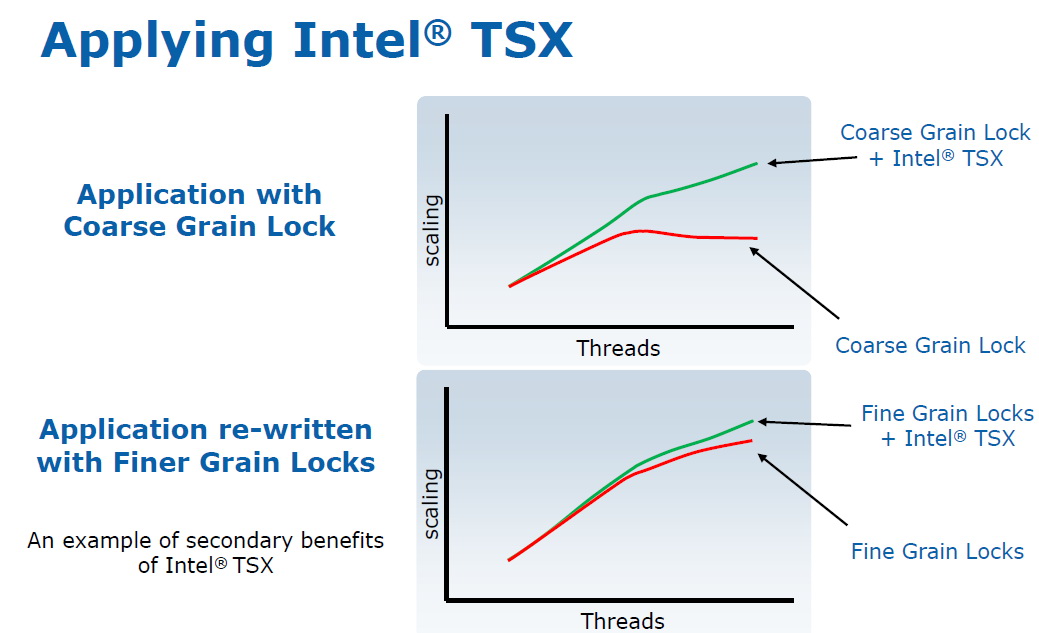

Если снятие или снятие блокировки прошло успешно, все потоки могут работать параллельно.Если нет, вы вернетесь к традиционной блокировке. Таким образом, разработчик может использовать грубую блокировку (например, блокировку всей совместно используемой структуры) в качестве «запасного» решения, в то время как Lock Elision может обеспечить производительность, которую могло бы получить программное обеспечение с хорошо настроенной библиотекой мелкозернистой блокировки.

По словам Рави и Мартина, прелесть состоит в том, что разработчик ваших библиотек блокировки просто должен добавить несколько инструкций HLE, не нарушая обратной совместимости. Разработчик использует новую библиотеку с поддержкой TSX и получает преимущества TSX, если его приложение запускается на Haswell или более позднем ЦП Intel.

Разработчик использует новую библиотеку с поддержкой TSX и получает преимущества TSX, если его приложение запускается на Haswell или более позднем ЦП Intel.

Включение или отключение возможности Intel TSX в Windows 10

РЕКОМЕНДУЕТСЯ: Нажмите здесь, чтобы исправить ошибки Windows и оптимизировать производительность системы

Microsoft опубликовала руководство, которое поможет пользователям защитить свои системы от отказа в обслуживании (DoS) и нарушений безопасности при раскрытии информации, связанной с процессорами Intel, о чем было объявлено в патче во вторник на этой неделе.

Уязвимость DoS, отслеживаемая в CVE-2018-12207, затрагивает базовые клиентские и серверные процессоры Intel вплоть до 8-го поколения, в то время как спекулятивная уязвимость, отслеживаемая в CVE-2019-11135, обнаруживается в возможности Intel Transactional Synchronization Extensions (TSX) для защиты процессоров Intel до 10-го поколения включительно, это незначительно.

Transactional Synchronization Extensions (TSX), также известные как Transactional Synchronization Extensions New Instructions (TSX-NI), являются расширением архитектуры набора команд x86 (ISA), которое добавляет поддержку аппаратной памяти транзакций и ускоряет выполнение многопоточных программное обеспечение через блокировку elision. На основе различных тестов TSX / TSX-NI может обеспечить примерно на 40% более быстрое выполнение приложений и в 4–5 раз больше транзакций базы данных в секунду (TPS) для определенных рабочих нагрузок.

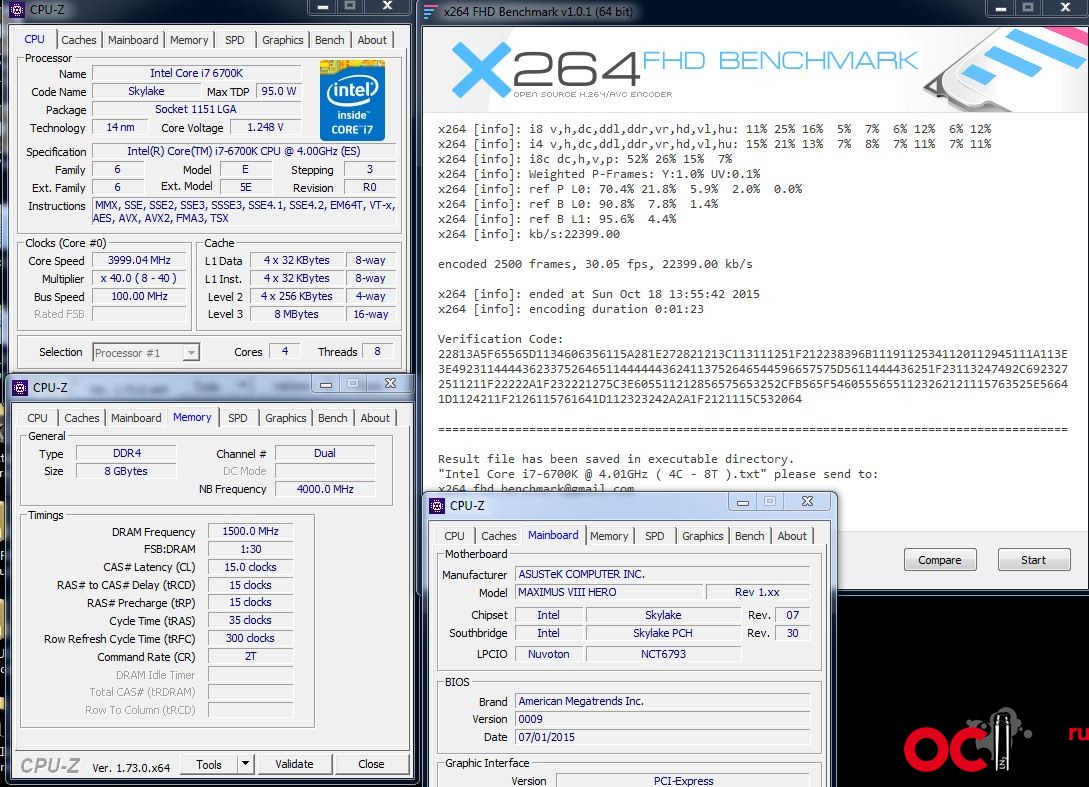

TSX / TSX-NI был задокументирован Intel в феврале 2012 года и был представлен в июне 2013 года на некоторых микропроцессорах Intel на базе микроархитектуры Haswell. Процессоры Haswell ниже 45xx и SKU серий R и K (с включенным множителем) не поддерживают TSX / TSX-NI. В августе 2014 года Intel объявила об ошибке в реализации TSX / TSX-NI на текущих уровнях процессоров Haswell, Haswell-E, Haswell-EP и ранних процессоров Broadwell, что привело к отключению функции TSX / TSX-NI на затронутые процессоры через обновление прошивки.

В 2016 году была обнаружена атака синхронизации по побочному каналу, в которой способ обработки TSX / TSX-NI ошибок транзакций (то есть ошибок страниц) был использован для взлома KASLR во всех основных операционных системах.

Поддержка эмуляции TSX / TSX-NI предоставляется как часть эмулятора разработки программного обеспечения Intel. Также имеется экспериментальная поддержка эмуляции TSX / TSX-NI в диапазоне QEMU.

Intel TSX предоставляет два программных интерфейса для указания областей кода для исполнения сделки.

Аппаратный замок Elision (HLE)

HLE — это совместимое с возрастом расширение набора команд (с префиксами XACQUIRE и XRELEASE) для указания регионов транзакций. HLE предназначен для программистов, которые предпочитают обратную совместимость традиционной взаимоисключающей модели программирования и хотят запускать HLE-совместимое программное обеспечение на старом оборудовании, но хотят воспользоваться преимуществами новых возможностей блокировки на оборудовании с поддержкой HLE.

Внутренние функции Hardware Lock Elision (HLE) применимы только к приложениям C / C ++ для Windows.

Память с ограничениями для транзакций (RTM)

RTM — это новый интерфейс набора команд (состоящий из инструкций XBEGIN, XEND и XABORT), который позволяет программистам определять поля транзакций более гибко, чем с HLE.

RTM предназначена для программистов, которые предпочитают гибкий интерфейс аппаратному обеспечению для выполнения транзакций.

Взаимодействие с другими людьми Обновление за январь 2021 года:Теперь мы рекомендуем использовать этот инструмент для устранения вашей ошибки. Кроме того, этот инструмент исправляет распространенные компьютерные ошибки, защищает вас от потери файлов, вредоносных программ, сбоев оборудования и оптимизирует ваш компьютер для достижения максимальной производительности.С помощью этого программного обеспечения вы можете быстро решить проблемы с вашим ПК и предотвратить их возникновение:

- Шаг 1: Загрузите PC Repair & Optimizer Tool (Windows 10, 8, 7, XP, Vista — Microsoft Gold Certified).

- Шаг 2: Нажмите « Начать сканирование », чтобы найти проблемы реестра Windows, которые могут вызывать проблемы с ПК.

- Шаг 3. Нажмите « Восстановить все », чтобы исправить все проблемы.

Включение или отключение Intel TSX в Windows 10

Отключите Intel® Transactional Synchronization Extensions (Intel® TSX), используя следующий параметр реестра:

reg добавить "HKEY_LOCAL_MACHINE \ SYSTEM \ CurrentControlSet \ Control \ Session Manager \ Kernel" / v DisableTsx / t REG_DWORD / d 1 / f

Перезагрузите компьютер, чтобы изменения вступили в силу.

Включите Intel® Transactional Synchronization Extensions (Intel® TSX) с помощью следующего параметра реестра:

reg добавить "HKEY_LOCAL_MACHINE \ SYSTEM \ CurrentControlSet \ Control \ Session Manager \ Kernel" / v DisableTsx / t REG_DWORD / d 0 / f

Перезагрузите компьютер, чтобы изменения вступили в силу.

https://news.ycombinator.com/item?id=21533791

РЕКОМЕНДУЕТСЯ: Нажмите здесь, чтобы устранить ошибки Windows и оптимизировать производительность системы

CCNA, веб-разработчик, средство устранения неполадок ПК

Я компьютерный энтузиаст и практикующий ИТ-специалист.У меня за плечами многолетний опыт программирования, поиска и устранения неисправностей оборудования и ремонта. Я специализируюсь на веб-разработке и проектировании баз данных. У меня также есть сертификат CCNA по проектированию сетей и устранению неполадок.

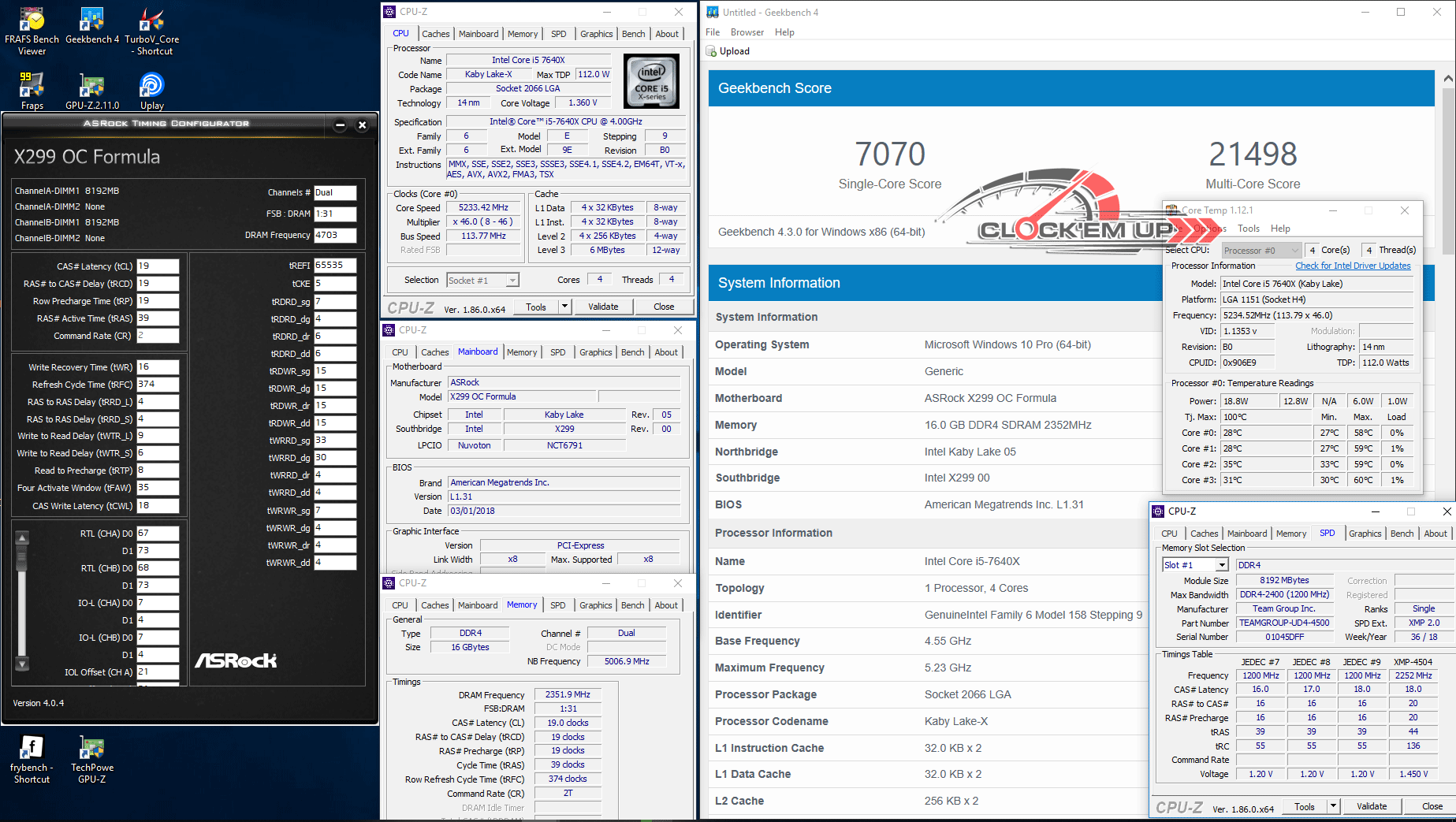

ПроизводительностьTSX — анализ возможностей Intel Haswell Transactional Synchronization eXtensions

TSX Производительность

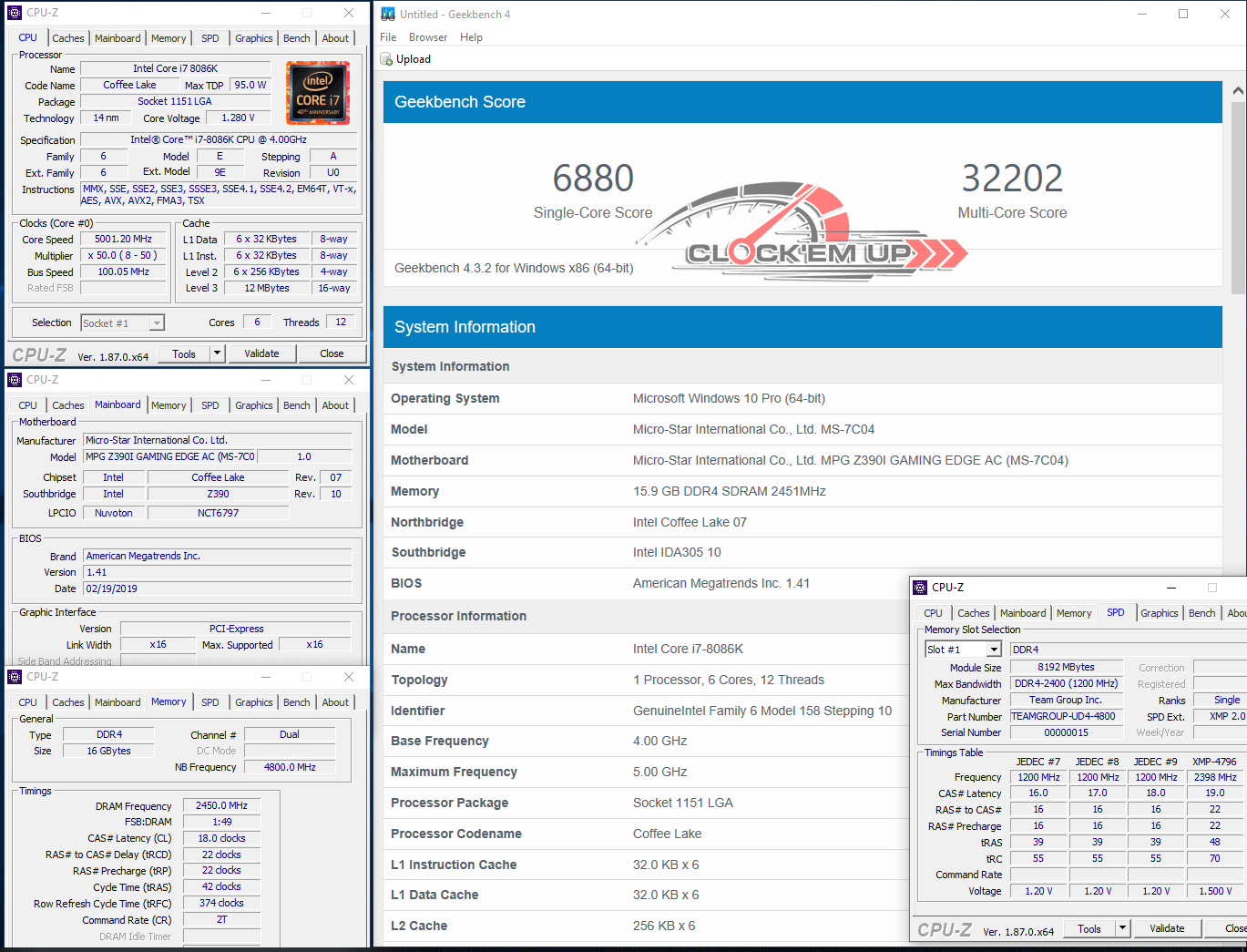

Рави и Мартинг дали расплывчатые, но все же довольно интересные данные о производительности:

Согласно Intel, использование приложения, которое ранее использовало грубую блокировку (например, более старые механизмы хранения MyISAM MySQL) вместе с библиотекой с поддержкой TSX, должно значительно улучшить масштабирование. Что интересно, даже приложения с мелкозернистыми блокировками должны выиграть от использования TSX. Поскольку TSX использует L1-кеш для буферизации записи (Дэвид Кантер подробно описывает это здесь) и не блокирует (если не выполняется повторное выполнение / откат), меньше активности памяти и особенно меньше трафика синхронизации. Или, другими словами, строки кэша меньше «разбрасываются».

Что интересно, даже приложения с мелкозернистыми блокировками должны выиграть от использования TSX. Поскольку TSX использует L1-кеш для буферизации записи (Дэвид Кантер подробно описывает это здесь) и не блокирует (если не выполняется повторное выполнение / откат), меньше активности памяти и особенно меньше трафика синхронизации. Или, другими словами, строки кэша меньше «разбрасываются».

В некоторых случаях HLE / RTM, конечно, не работает. «ЦП выполняет мелкозернистую блокировку» основан на маркировке строк кэша L1 (64 Б), и их 512, чтобы быть конкретными (64 x 512 = 32 КБ).Для каждой строки кэша существует только один «тег блокировки». Более чем одна блокировка одной и той же строки кэша вызовет прерывание HLE / RTM, поскольку в этом случае ЦП не может отслеживать две блокировки по отдельности.

Во-вторых, все «подлежащие блокировке» переменные фрагмента кода, поддерживающего TSX, должны быть помещены в L1-кэш. Если часть критического кода должна заблокировать переменные из более чем 8 строк кэша, которые все отображаются в слоты одного и того же набора, HLE не будет работать: L1 является 8-сторонним ассоциативным набором. Все, что прерывает транзакцию, прерывает транзакцию: немаскированные прерывания (прерывания, которые нельзя игнорировать), выходы виртуальной машины, сбои… список можно продолжить. Тем не менее, есть много случаев, когда TSX определенно может помочь, и код может быть написан с учетом требований и ограничений.

Все, что прерывает транзакцию, прерывает транзакцию: немаскированные прерывания (прерывания, которые нельзя игнорировать), выходы виртуальной машины, сбои… список можно продолжить. Тем не менее, есть много случаев, когда TSX определенно может помочь, и код может быть написан с учетом требований и ограничений.

Заключение

TSX будет поддерживаться GCC v4.8, последней версией Microsoft Visual Studio 2012 и, конечно же, компилятором C Intel v13. Также доступна поддержка GLIBC (ветка rtm-2.17). Итак, похоже, что программная экосистема готова для TSX. Самое крутое в TSX (особенно HLE) заключается в том, что он позволяет хорошо масштабировать наши текущие многоядерные процессоры без огромных затрат времени на точную настройку блокировок.Другими словами, он может дать разработчикам «высокую производительность при крупных усилиях», как любит выражаться Intel.

Теоретически большинству разработчиков приложений даже не нужно будет изменять свой код, кроме ссылки на библиотеку с поддержкой TSX. Время покажет, будет ли в большинстве случаев так просто разблокировать хорошее многоядерное масштабирование. Если все пойдет по плану Intel, TSX может позволить гораздо большему разнообразию программного обеспечения воспользоваться преимуществами постоянно растущего числа ядер на наших серверах, настольных компьютерах и портативных устройствах.

Время покажет, будет ли в большинстве случаев так просто разблокировать хорошее многоядерное масштабирование. Если все пойдет по плану Intel, TSX может позволить гораздо большему разнообразию программного обеспечения воспользоваться преимуществами постоянно растущего числа ядер на наших серверах, настольных компьютерах и портативных устройствах.

Объяснение расширений транзакционной синхронизации

Transactional Synchronization Extensions ( TSX ), также называемые Transactional Synchronization Extensions New Instructions ( TSX-NI ), является расширением архитектуры набора инструкций x86 (ISA), которое добавляет поддержку аппаратной транзакционной памяти, ускоряя выполнение многопоточного программного обеспечения через блокировку. Согласно различным тестам, TSX / TSX-NI может обеспечить примерно на 40% более быстрое выполнение приложений при определенных рабочих нагрузках и в 4–5 раз больше транзакций базы данных в секунду (TPS). [1] [2] [3] [4]

[1] [2] [3] [4]

TSX / TSX-NI был задокументирован Intel в феврале 2012 года и дебютировал в июне 2013 года на отдельных микропроцессорах Intel на основе микроархитектуры Haswell. [5] [6] [7] Процессоры Haswell ниже 45xx, а также SKU серий R и K (с разблокированным множителем) не поддерживают TSX / TSX-NI. [8] В августе 2014 года Intel объявила об ошибке в реализации TSX / TSX-NI на текущих степпингах Haswell, Haswell-E, Haswell-EP и ранних CPU Broadwell, что привело к отключению функции TSX / TSX-NI. на затронутых процессорах через обновление микрокода. [9] [10]

В 2016 году была обнаружена временная атака по побочному каналу путем злоупотребления способом TSX / TSX-NI обрабатывать транзакционные ошибки (то есть ошибки страниц) для взлома KASLR во всех основных операционных системах. [11] .

Поддержка эмуляции TSX / TSX-NI предоставляется как часть эмулятора разработки программного обеспечения Intel. [12] Существует также экспериментальная поддержка эмуляции TSX / TSX-NI в ответвлении QEMU. [13]

Характеристики

TSX / TSX-NI предоставляет два программных интерфейса для обозначения областей кода для выполнения транзакций. Hardware Lock Elision (HLE) — это интерфейс на основе префиксов команд, предназначенный для обратной совместимости с процессорами без поддержки TSX / TSX-NI. Ограниченная транзакционная память (RTM) — это новый интерфейс набора команд, который обеспечивает большую гибкость для программистов. [14]

TSX / TSX-NI обеспечивает оптимистичное выполнение областей транзакционного кода. Аппаратное обеспечение отслеживает несколько потоков на предмет конфликтующих обращений к памяти, прерывая и откатывая транзакции, которые не могут быть успешно завершены.Для программного обеспечения предусмотрены механизмы обнаружения и обработки неудачных транзакций.

Другими словами, снятие блокировки посредством выполнения транзакции использует транзакции памяти как быстрый путь, где это возможно, в то время как медленный (резервный) путь по-прежнему является нормальной блокировкой.

Аппаратный замок Elision

Hardware Lock Elision (HLE) добавляет два новых префикса команд: XACQUIRE и XRELEASE . Эти два префикса повторно используют коды операций существующих префиксов REPNE / REPE ( F2H / F3H ).На процессорах, которые не поддерживают TSX / TSX-NI, префиксы REPNE / REPE игнорируются в инструкциях, для которых действительны XACQUIRE / XRELEASE , что обеспечивает обратную совместимость. [15]

Подсказка префикса XACQUIRE может использоваться только со следующими инструкциями с явным префиксом LOCK : ADD , ADC , AND , BTC , BTR , BTS , CMPXCHG , CMPXCHG8B , DEC , INC , NEG , NOT , OR , SBB , SUB , XOR , XADD и XCHG .Инструкцию XCHG можно также использовать без префикса LOCK .

Подсказка префикса XRELEASE может использоваться как с инструкциями, перечисленными выше, так и с инструкциями MOV mem, reg и MOV mem, imm .

HLE позволяет оптимистично выполнить критический раздел, пропуская запись в блокировку, так что блокировка кажется свободной для других потоков. Неудачная транзакция приводит к перезапуску выполнения из инструкции с префиксом XACQUIRE , но обрабатывает инструкцию так, как если бы префикс XACQUIRE отсутствовал.

Ограниченная транзакционная память

Ограниченная транзакционная память (RTM) — это альтернативная реализация HLE, которая дает программисту гибкость в указании пути резервного кода, который выполняется, когда транзакция не может быть успешно выполнена.

RTM добавляет три новые инструкции: XBEGIN , XEND и XABORT . Команды XBEGIN и XEND отмечают начало и конец области кода транзакции; инструкция XABORT явно прерывает транзакцию.Ошибка транзакции перенаправляет процессор на путь резервного кода, указанный инструкцией XBEGIN , при этом статус прерывания возвращается в регистре EAX .

| Регистр EAX позиция бита | Значение | |

|---|---|---|

| 0 | Устанавливается, если прерывание вызвано инструкцией XABORT . | |

| 1 | Если установлено, транзакция может быть успешной при повторной попытке. Этот бит всегда сброшен, если установлен бит 0. | |

| 2 | Устанавливается, если другой логический процессор конфликтует с адресом памяти, который был частью транзакции, которая была прервана. | |

| 3 | Устанавливается, если внутренний буфер переполнен. | |

| 4 | Устанавливается, если сработала точка останова отладки. | |

| 5 | Устанавливается, если во время выполнения вложенной транзакции произошло прерывание. | |

| 23: 6 | Зарезервировано. | |

| 31:24 | XABORT аргумент (действителен, только если установлен бит 0, в противном случае зарезервирован). |

XTEST инструкция TSX / TSX-NI предоставляет новую команду XTEST , которая возвращает, выполняет ли процессор транзакционную область.

Реализация

Спецификация Intel TSX / TSX-NI описывает, как транзакционная память предоставляется программистам, но не раскрывает подробностей о фактической реализации транзакционной памяти. [16] Intel указывает в своих руководствах по разработке и оптимизации, что Haswell поддерживает наборы для чтения и записи с детализацией строки кэша, отслеживая адреса в кэше данных L1 процессора. [17] [18] [19] [20] Intel также заявляет, что конфликты данных обнаруживаются с помощью протокола согласованности кэша.

Кэш данных L1Haswell имеет ассоциативность восемь. Это означает, что в этой реализации транзакционное выполнение, которое записывает в девять различных местоположений, отображаемых в один и тот же набор кешей, будет прервано. Однако из-за микроархитектурных реализаций это не означает, что меньшее количество обращений к одному и тому же набору гарантированно никогда не прервется.Кроме того, в конфигурациях ЦП с технологией Hyper-Threading кэш L1 совместно используется двумя потоками в одном ядре, поэтому операции в логическом процессоре одного уровня с тем же ядром могут вызывать вытеснение.

Независимые исследования указывают на то, что транзакционная память Haswell, скорее всего, представляет собой систему отложенного обновления, использующую кеши для каждого ядра для транзакционных данных и контрольные точки регистрации. Другими словами, Haswell с большей вероятностью будет использовать систему транзакционной памяти на основе кеша, поскольку это гораздо менее рискованный вариант реализации.С другой стороны, Intel Skylake или более поздняя версия может комбинировать этот подход на основе кеширования с буфером упорядочения памяти (MOB) для той же цели, возможно, также обеспечивая многоверсионную транзакционную память, которая больше поддается спекулятивной многопоточности. [21]